# **Soldering and Mounting Techniques**

Reference Manual

SOLDERRM/D Rev. 6, September–2008

© SCILLC, 2008 "All Rights Reserved"

FULLPAK, ICePAK, MicroIntegration, MicroLeadless, MOSORB, MiniMOSORB, and POWERTAP are trademarks of Semiconductor Components Industries, LLC (SCILLC). Cho-Therm is a registered trademark of Chromerics, Inc. Grafoil is a registered trademark of Union Carbide. Kapton is a registered trademark of du Pont de Nemours & Co., Inc. Kon-Dux and Rubber-Duc are trademarks of Aavid Thermal Technologies, Inc. PowerFLEX is a trademark of Texas Instruments Incorporated. Thermasil is a registered trademark and Thermafilm is a trademark of Thermalloy, Inc. Micro8 is a trademark of International Rectifier. Intel and Pentium are registered trademarks and Itanium is a trademark of Intel Corporation. ChipFET is a trademark of Vishay Siliconix. POWERMITE is a registered trademark of and used under a license from Microsemi Corporation.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

### **SOLDERRM**

# **Table of Contents**

| Section 1:                               |                               |                              |

|------------------------------------------|-------------------------------|------------------------------|

| General Pb (Lead) Free Lead Finish/      | Plating Strategy              | 5                            |

| Section 2:                               |                               |                              |

| Soldering/Mounting Techniques            |                               | 9                            |

|                                          |                               |                              |

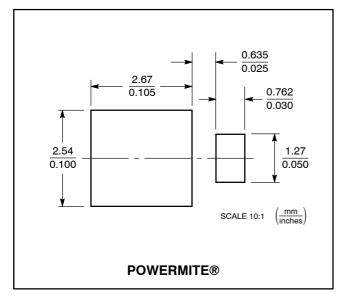

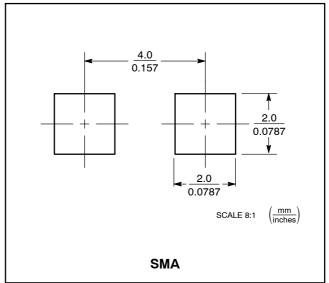

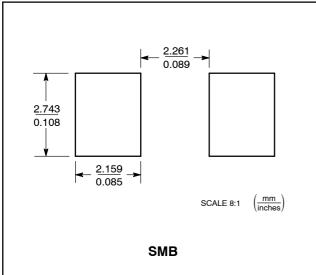

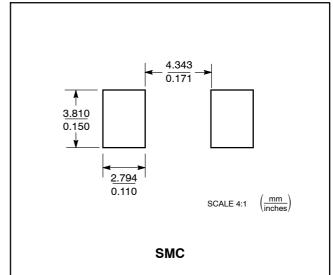

| POWERMITE® 14                            | SMA 14                        | SMB 14                       |

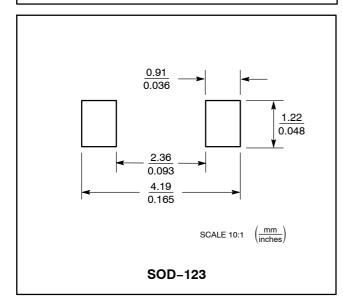

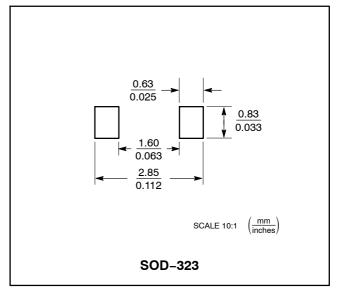

| SMC 14                                   | SOD-123 14                    | SOD-323 14                   |

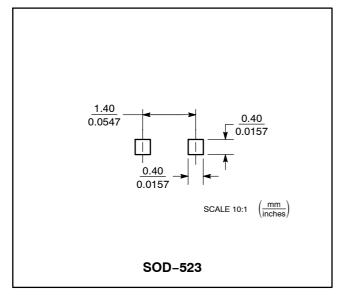

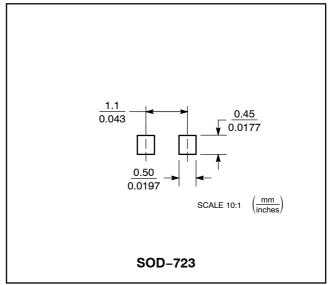

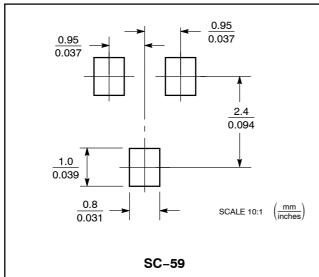

| SOD-523 15                               | SOD-723 15                    | SC-59 15                     |

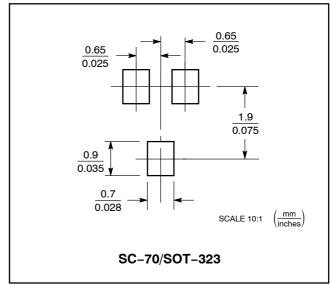

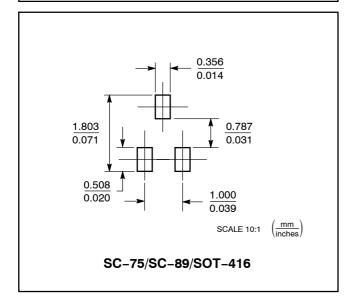

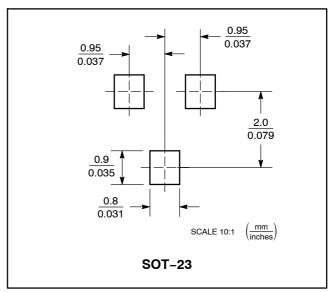

| SC-70/SOT-323                            | SC-75/SC-89/SOT-416 15        | SOT-23 15                    |

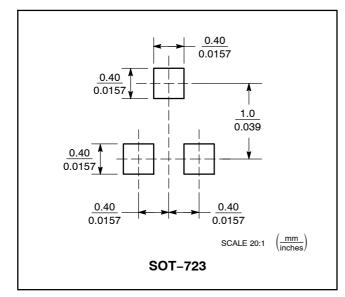

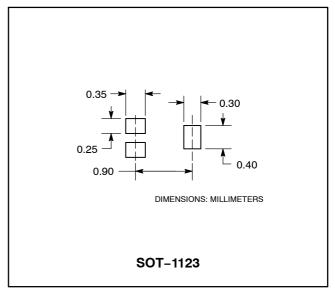

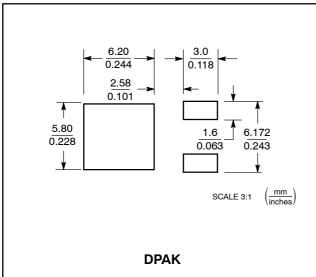

| SOT-723 16                               | SOT-1123 16                   | DPAK 16                      |

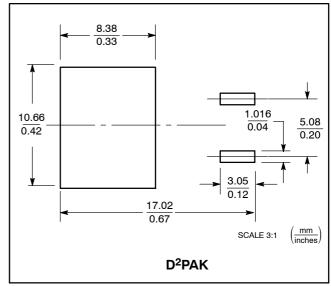

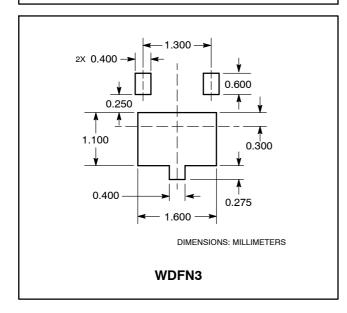

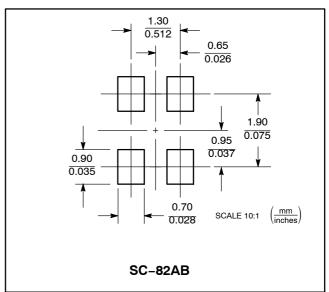

| D <sup>2</sup> PAK                       | WDFN3 16                      | SC-82AB 16                   |

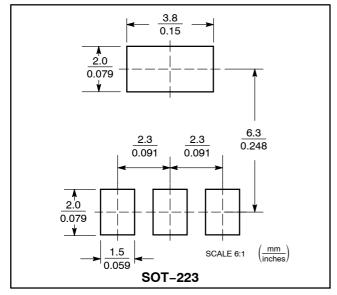

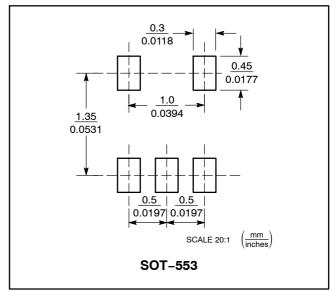

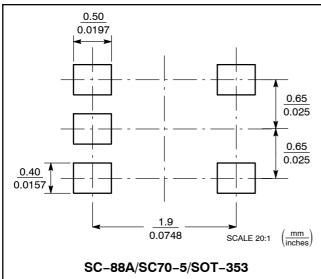

| SOT-223 17                               | SOT-553 17                    | SC-88A/SC70-5/SOT-353 17     |

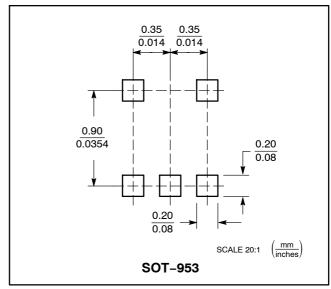

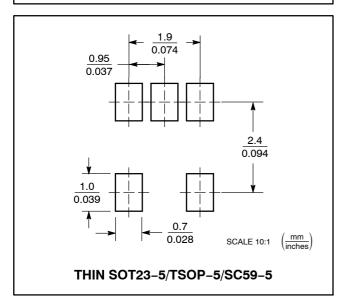

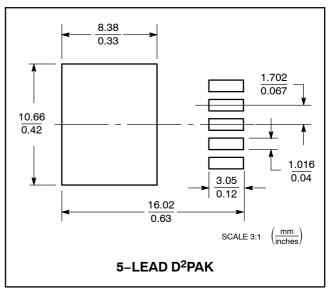

| SOT-953 17                               | THIN SOT23-5/TSOP-5/SC59-5 17 | 5–LEAD D <sup>2</sup> PAK    |

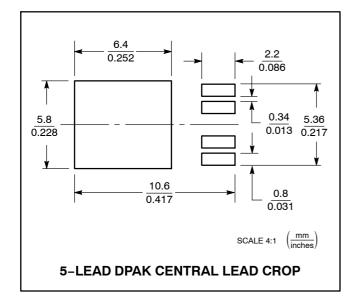

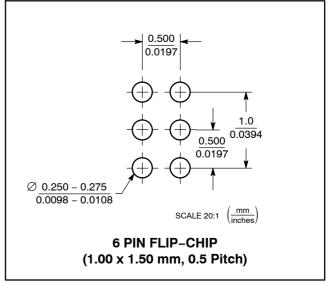

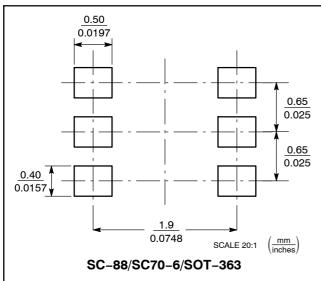

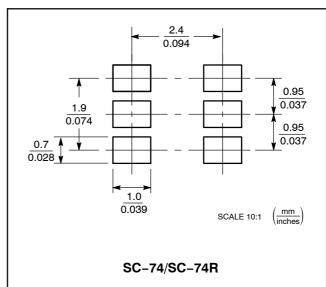

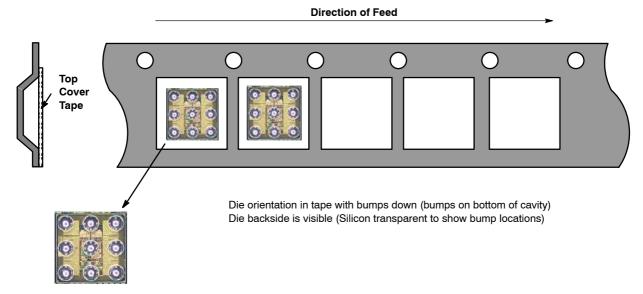

| 5-LEAD DPAK Central Lead Crop 18         | 6-PIN FLIP-CHIP               | SC-88/SC70-6/SOT-363 18      |

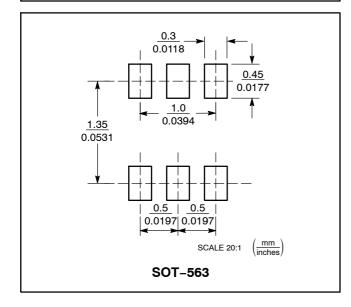

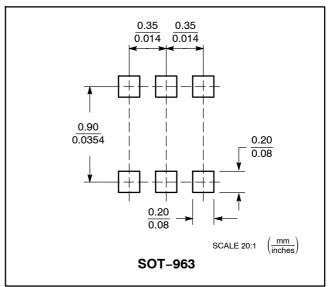

| SC-74/SC-74R                             | SOT-563 18                    | SOT-963 18                   |

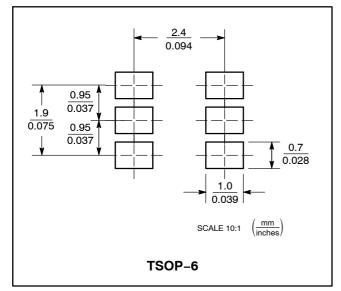

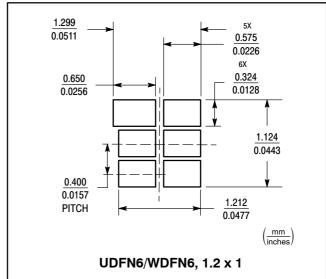

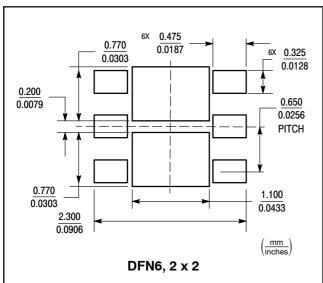

| TSOP-619                                 | UDFN6/WDFN6, 1.2 x 1 19       | DFN6, 2 x 2                  |

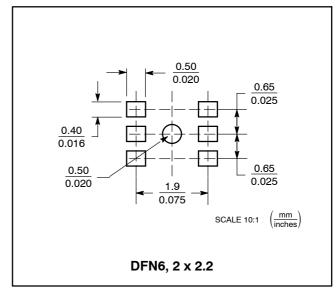

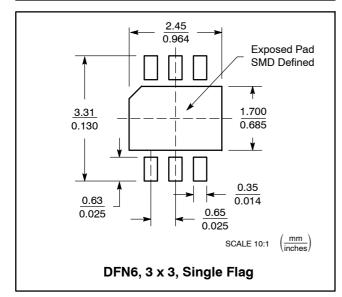

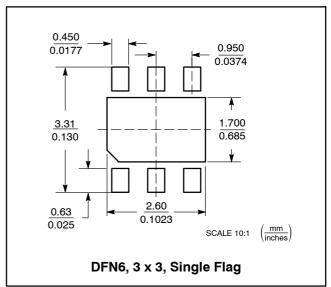

| DFN6, 2 x 2.2                            | DFN6, 3 x 3, Single Flag      | DFN6, 3 x 3, Single Flag     |

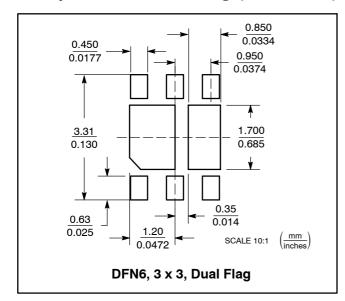

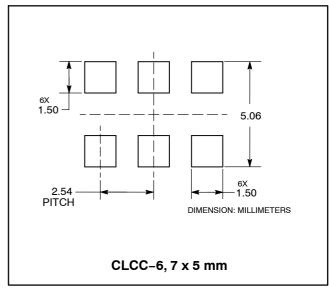

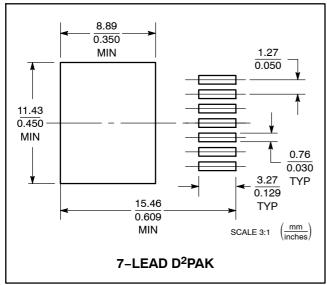

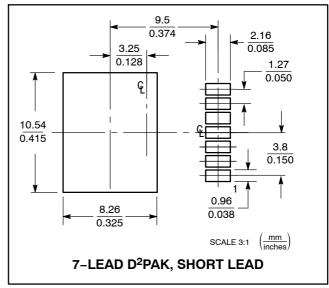

| DFN6, 3 x 3, Dual Flag 20                | CLCC-6 20                     | 7-LEAD D <sup>2</sup> PAK 20 |

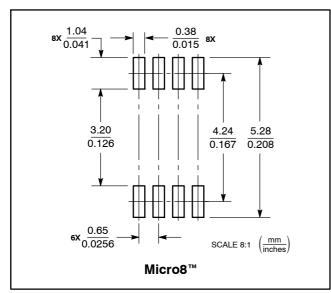

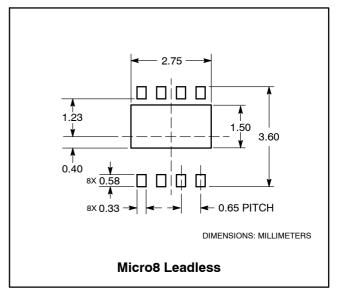

| 7-LEAD D <sup>2</sup> PAK, Short Lead 20 | Micro8 <sup>™</sup>           | Micro8 Leadless 20           |

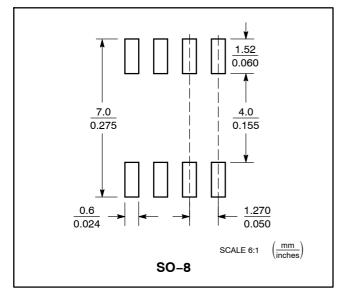

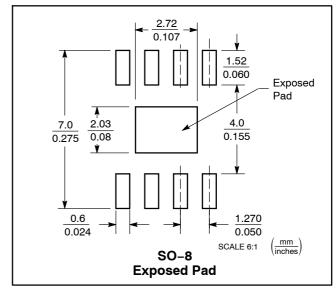

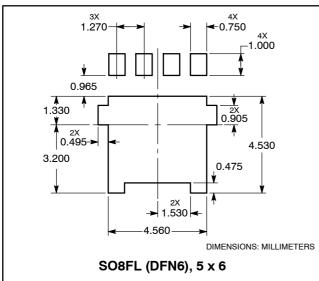

| SO-821                                   | SO-8 Exposed Pad              | SO8FL (DFN6), 5 x 6          |

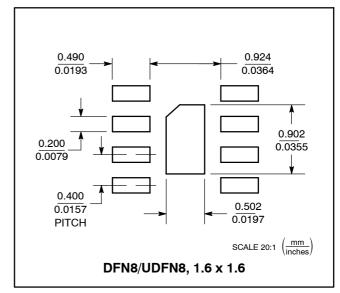

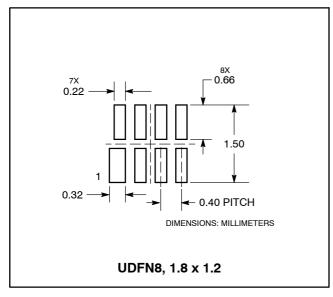

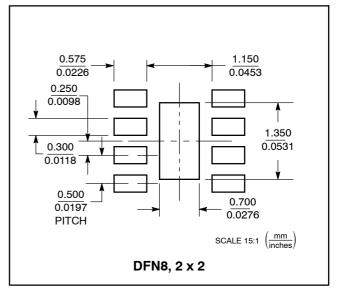

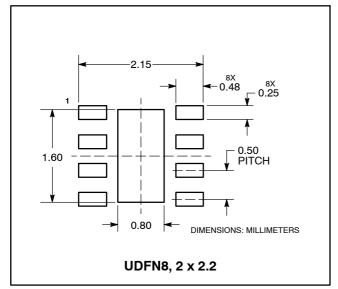

| DFN8/UDFN8, 1.6 x 1.6 21                 | UDFN8, 1.8 x 1.2              | DFN8, 2 x 2                  |

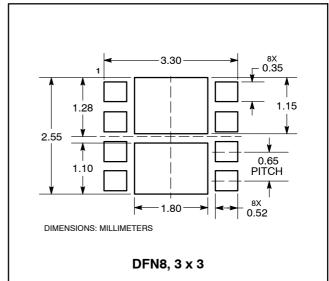

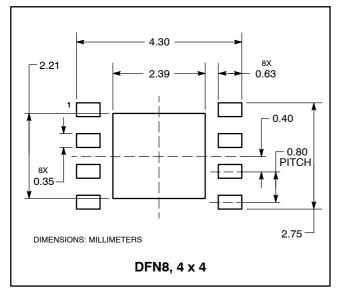

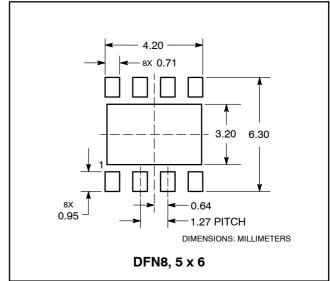

| UDFN8, 2 x 2.2                           | DFN8, 3 x 3                   | DFN8, 4 x 4                  |

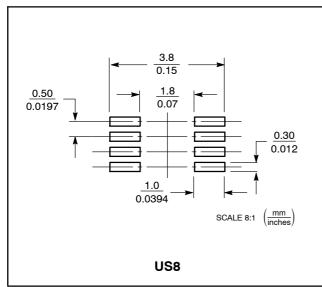

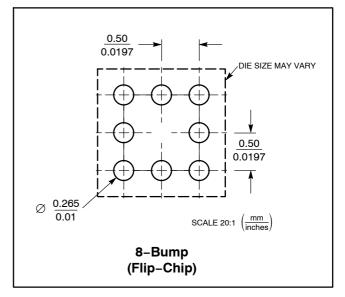

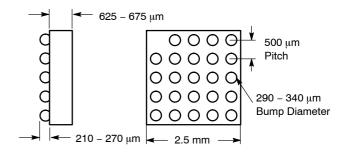

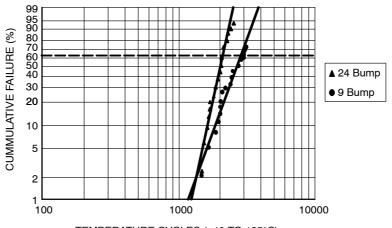

| DFN8, 5 x 6                              | US8 22                        | 8–Bump (Flip–Chip)           |

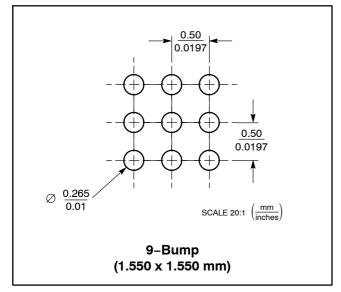

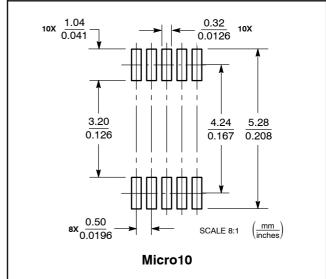

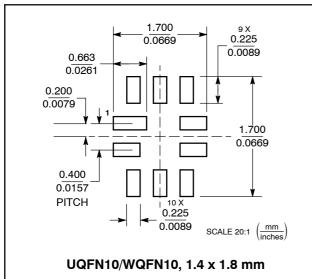

| 9-Bump 23                                | Micro10                       | UQFN10/WQFN10, 1.4 x 1.8 23  |

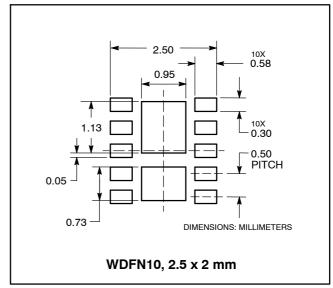

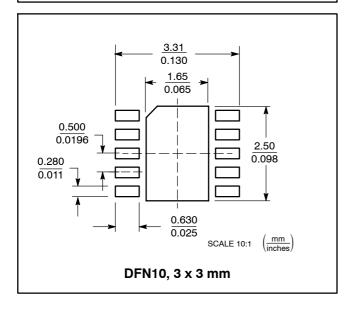

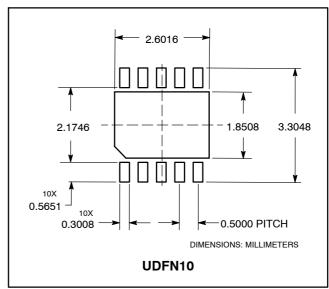

| WDFN10, 2.5 x 2 23                       | DFN10, 3 x 3                  | UDFN10 23                    |

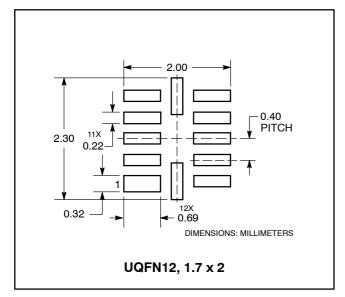

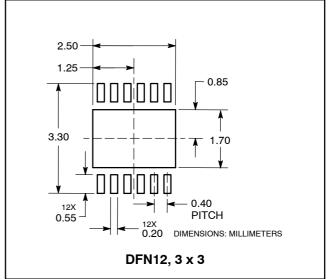

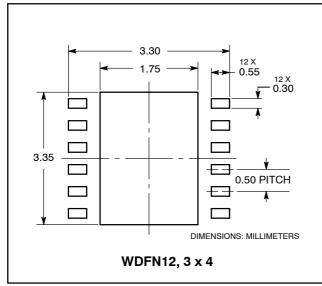

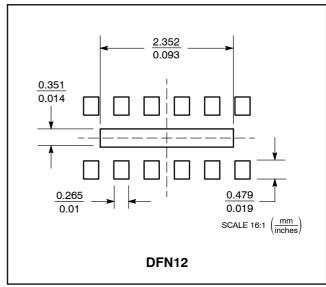

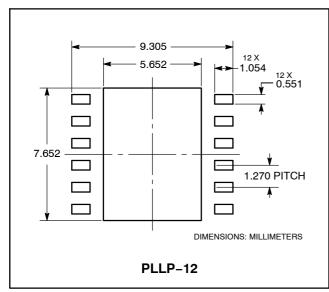

| UQFN12, 1.7 x 2 24                       | DFN12, 3 x 3 24               | WDFN12, 3 x 4 24             |

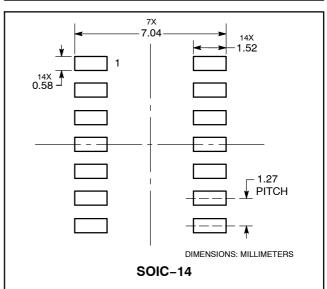

| DFN12 24                                 | PLLP-12                       | SOIC-1424                    |

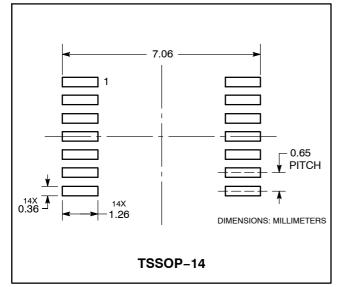

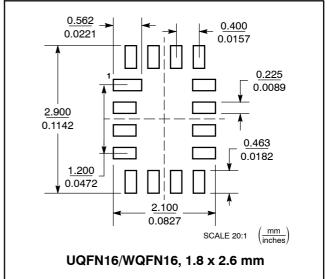

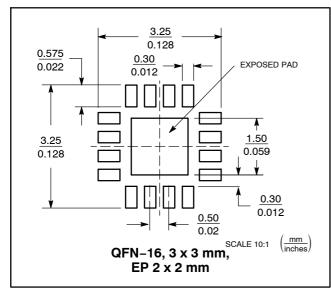

| TSSOP-14 25                              | UQFN16/WQFN16, 1.8 x 2.6 25   | QFN-16, 3 x 3/EP, 2 x 2      |

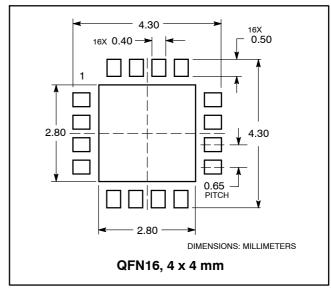

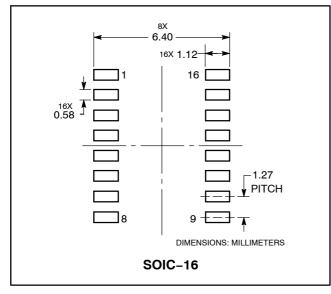

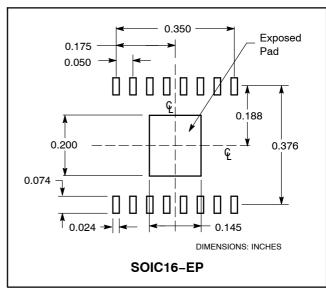

| QFN16, 4 x 4                             | SOIC-16                       | SOIC16-EP                    |

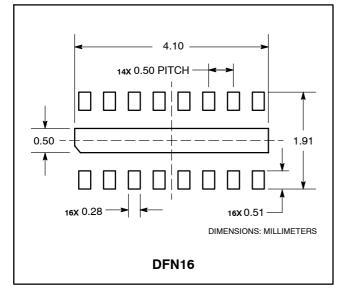

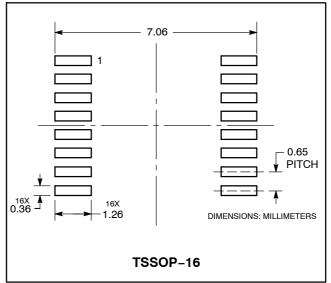

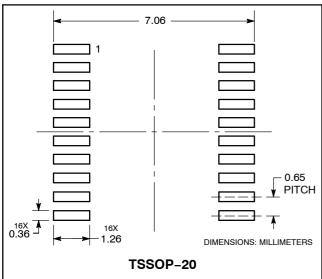

| DFN16 26                                 | TSSOP-16                      | TSSOP-20 26                  |

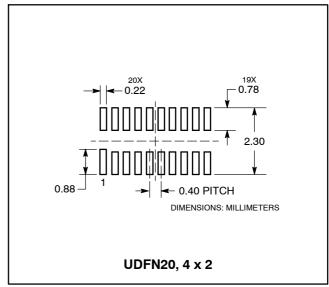

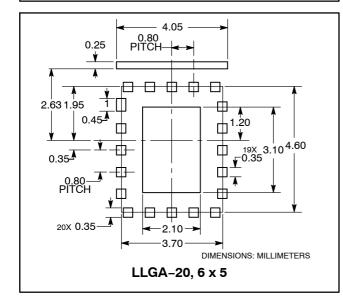

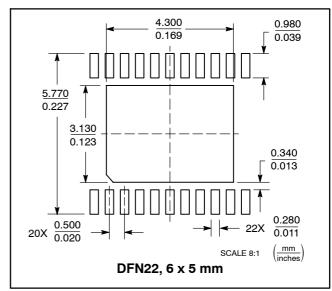

| UDFN20, 4 x 2                            | LLGA-20, 6 x 5 26             | DFN22, 6 x 5                 |

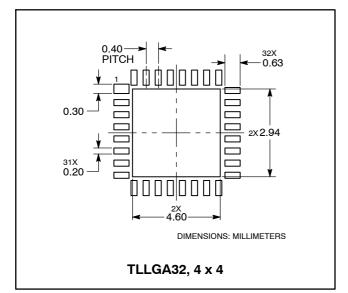

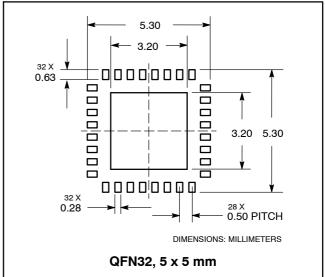

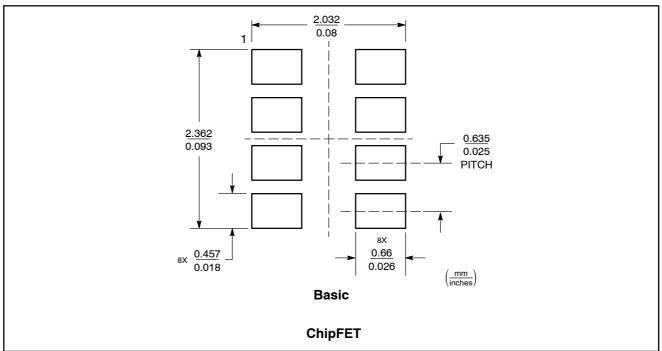

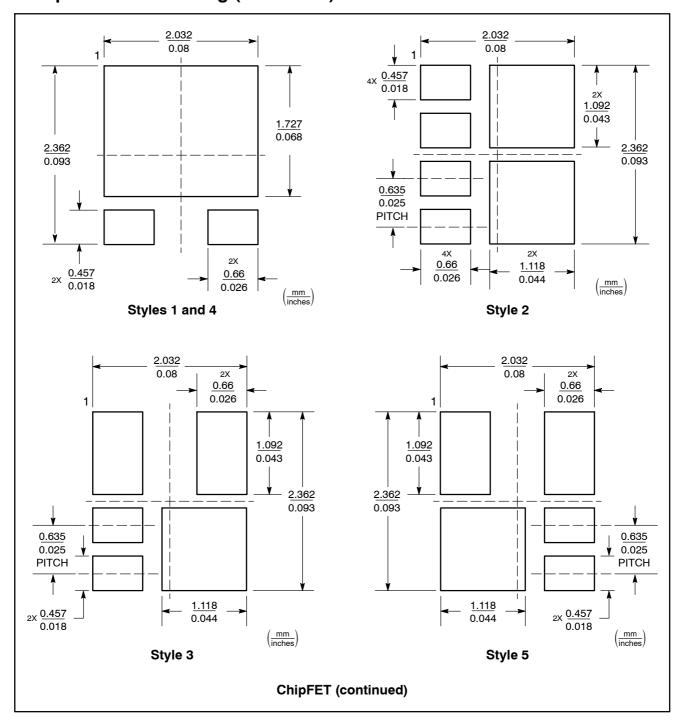

| TLLGA32, 4 x 4 27                        | QFN32, 5 x 5 27               | ChipFET                      |

| Mounting Considerations for Power        | Semiconductors                |                              |

| Section 3:                               |                               |                              |

| Handling of Semiconductor Packages       | S                             |                              |

| Section 4:                               |                               |                              |

| Semiconductor Package Reliability as     | nd Quality                    |                              |

| Section 5:                               | -                             |                              |

| Device Rework / Removal                  |                               |                              |

**SOLDERRM**

# Section 1

General Pb (Lead) Free Lead Finish/ Plating Strategy

# General Pb (Lead) Free Lead Finish/Plating Strategy

In order to provide maximum flexibility and convenience for our customers, ON Semiconductor is modifying its strategy to support the Pb–free global initiatives from the previous General Announcement #12770.

**Pb-free Plating Strategy** – ON Semiconductor now offers a portfolio of devices that are plated with Pb-free lead finishes. Many of our products were originally released as Pb-free and do not have a comparable leaded version available. For devices which have been Pb-free since their inception, we do not intend to introduce any new Pb-containing lead finish versions of those devices.

For those customers that choose not to convert to our Pb-free offering according to our conversion plan, ON Semiconductor will continue to offer the current Pb containing devices until business conditions no longer prove feasible. We are committed to meeting the needs of all of our customers as our industry transitions to Pb-free over the next couple of years.

ON Semiconductor has qualified the majority of our packages in the Pb-free version and have made them available for sampling and production ordering. The list below shows the packages that have been qualified and the few remaining with their targeted completion dates. Please contact your ON Semiconductor Sales Representative if this schedule does not meet your conversion needs, or if you want to order Pb-free samples.

ON Semiconductor is fully compliant with the RoHS directive for all of the parts for which it makes business sense to do so. In other words, ON Semiconductor offers

Pb-free versions of all of the parts for which there is sufficient demand. We will also continue to offer all of these parts in a standard Tin-Lead (SnPb) lead finish until market conditions necessitate a change in direction.

Moisture Sensitivity Level (MSL) – Surface Mount Packages are qualified to 260°C, which is compliant to the JEDEC standard J–STD–020C. The majority of the MSL ratings will remain unchanged from the current MSL 1 classification. If there is a change in the MSL rating of a package, the customer will be notified and appropriate packing precautions will be taken before any product is shipped by ON Semiconductor.

Product Identification - Devices offered without a Pb containing lead finish will be concatenated with a "G" suffix to denote Pb-free lead finish and qualified compatibility with Pb-free board mount assembly processing. Existing packages that are currently offered solely with a Pb-free finish will also change part numbers. This is intended to clearly identify parts that are Pb-free and qualified for compatibility with Pb-free board mount assembly processing. The MPN (Manufacturer Part Number) bar code label on the reel, tube or rail, and the intermediate boxes will have the "Pb-free 2LI" logo printed on those labels compliant to JEDEC standard JESD97. Pb-free products may also be identified by unique product marking. Pb-free products are marked with a G suffix to the part number on the package. However, if the package is too small to include the additional G character, the Pb-free package will be marked with a micro dot.

| Available Now                         |                        |                       |                        |

|---------------------------------------|------------------------|-----------------------|------------------------|

| Axial Lead Button                     | POWERMITE™             | SO-8                  | SSOP                   |

| Case 77                               | POWERTAP™              | SOD-123               | SSOVP                  |

| ChipFET™                              | PSOP-2                 | SOD-323               | Surge Special          |

| D <sup>2</sup> PAK 3, 5, 7            | QFN 5x5, 5x6, 7x7, 8x8 | SOD-523               | Surmetic               |

| D <sup>2</sup> PAK Discrete           | QFN 2x2.2, 3x3, 4x4    | SOEIAJ 8/14/16/20     | TO-218                 |

| DFN 1.6x1.6, 3x1, 3x3, 3.3x3.3, 4x1.6 | SC-59                  | SOIC Narrow 7/8/14/16 | TO-220 3/5/7           |

| DPAK                                  | SC-70 3/5              | SOIC Wide 16/18/20/24 | TO-247                 |

| FCDCA                                 | SC-74                  | SOIC 16W EP           | TO-264                 |

| LQFP 32/52                            | SC-75                  | SON 6 B/S             | TO-3                   |

| LQFP 52/64 EP                         | SC-82AB                | SOT-223               | TO-92                  |

| Micro8 <sup>™</sup> /10 IC            | SC-82 Dual             | SOT-23 3 Pin          | Top Can                |

| Micro8 FET                            | SC-88                  | SOT-23 5 Pin          | TQFP 48 EP             |

| Micro Leadless 3                      | SC-88A                 | SOT-23 6 Pin          | TSOP-5                 |

| MOSORB™/MiniMOSORB™                   | SC-89                  | SOT-23-L              | TSOP-6                 |

| PDIP 7/8/14/16/18/20/24N/24W          | SIDAC 1 & 3 Amp        | SOT-553               | TSSOP 8/14/16/20/24/48 |

| Available Now                  |                    |         |        |

|--------------------------------|--------------------|---------|--------|

| PLCC 20/28/44                  | SMA & SMA B/S      | SOT-563 | US8    |

| SMB                            | SOT-723 PowerFLEX™ | SMC     | SOT-89 |

| Planned                        |                    |         |        |

| FCBGA 16/49 SOIC 32W SPAK 5/7  |                    |         |        |

| Not Planned                    |                    |         |        |

| BGA CLCC QSOP CDIP PLLP (PQFN) | SOT-143            |         |        |

### **Qualification Plan:**

The qualification requirements for Pb-free external lead finish differ for surface-mount device (SMD) or through-hole devices (THD).

For the THDs the primary qualification requirement is to demonstrate forward compatibility with new Pb-free solder pastes (based on SnCuAg). The tests performed typically include:

- Solderability with SnCuAg solder

- Resistance to Solder Heat

For the SMDs reclassification of the moisture sensitivity level (MSL) at a peak reflow temperature of 260°C is required in addition to solderability validation. The MSL reclassification is performed on the largest die size that is used in the package. The tests performed typically include:

- Preconditioned Highly Accelerated Stress Testing (PC-HAST) – 96 hours minimum

- Preconditioned Autoclave (PC-AC) 96 hours minimum

- Preconditioned Temperature Cycling (PC-TC) 500 cycles minimum

- (Preconditioning is performed at the target MSL for 260 +5/-0°C)

- Solderability with SnCuAg solder

- Resistance to Solder Heat (RSH Solder Immersion)

### **Backward Compatibility**

Backward compatibility is the capability for our customers to take one of our Pb-free products, mount it on their PC board and reflow it using solder containing lead (Pb). ON Semiconductor has conducted reflow tests of Pb-free parts using leaded solder reflow temperatures and processes to simulate this condition. Tests have been conducted at 210 to 230°C and results show that there will not be solderability issues.

Please Note: This does not apply to BGA, bumped die or Flip-Chip devices. If the parts are Pb-free they need to use a Pb-free reflow process.

### **Points of Contact:**

- Your Local ON Semiconductor Sales Representative

- ON Semiconductor Technical Information Center 1–800–282–9855 (US & Canada) or via web at http://www.onsemi.com/tech-support

- http://www.onsemi.com/pb-free

| SOLDERRM |  |  |

|----------|--|--|

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

# Section 2

Soldering / Mounting Techniques

# **Soldering Considerations for Surface Mount Packages**

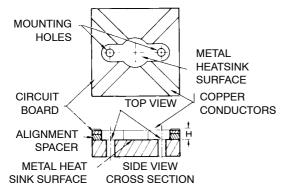

### RECOMMENDED FOOTPRINTS FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to ensure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

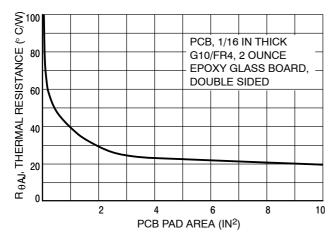

### POWER DISSIPATION FOR A SURFACE MOUNT DEVICE

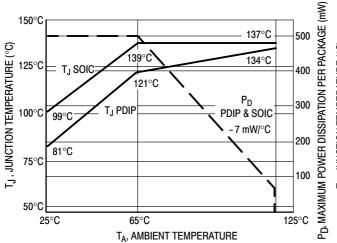

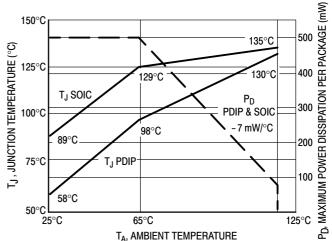

The power dissipation for a surface mount device is a function of the drain/collector pad size. These can vary from the minimum pad size for soldering to a pad size given for maximum power dissipation. Power dissipation for a surface mount device is determined by  $T_{J(max)}$ , the maximum rated junction temperature of the die,  $R_{\theta JA}$ , the thermal resistance from the device junction to ambient, and the operating ambient temperature,  $T_A$ . Using the values provided on the data sheet,  $P_D$  can be calculated as follows:

$$P_{D} = \frac{T_{J(max)} - T_{A}}{R_{\theta JA}}$$

The values for the equation are found in the maximum ratings table on the data sheet. Substituting these values into the equation for an ambient temperature  $T_A$  of 25°C, one can calculate the power dissipation of the device. For example, for a SOT–223 device,  $P_D$  is calculated as follows.

$$P_D = \frac{150^{\circ}C - 25^{\circ}C}{156^{\circ}C/W} = 800 \text{ milliwatts}$$

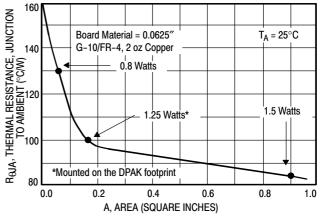

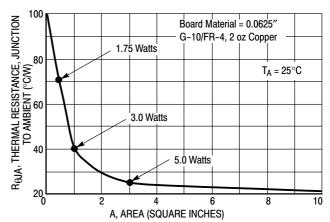

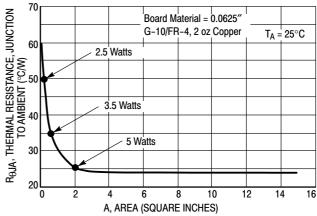

The 156°C/W for the SOT–223 package assumes the use of the recommended footprint on a glass epoxy printed circuit board to achieve a power dissipation of 800 milliwatts. There are other alternatives to achieving higher power dissipation from the surface mount packages. One is to increase the area of the drain/collector pad. By increasing the area of the drain/collector pad, the power dissipation can be increased. Although the power dissipation can almost be doubled with this method, area is taken up on the printed circuit board which can defeat the purpose of using surface mount technology. For example, a graph of  $R_{\theta JA}$  versus drain pad area is shown in Figures 1, 2 and 3.

Another alternative would be to use a ceramic substrate or an aluminum core board such as Thermal Clad<sup>TM</sup>. Using a board material such as Thermal Clad, an aluminum core board, the power dissipation can be doubled using the same footprint.

Figure 1. Thermal Resistance versus Drain Pad Area for the SOT-223 Package (Typical)

Figure 2. Thermal Resistance versus Drain Pad Area for the DPAK Package (Typical)

Figure 3. Thermal Resistance versus Drain Pad Area for the D<sup>2</sup>PAK Package (Typical)

### **SOLDER STENCIL GUIDELINES**

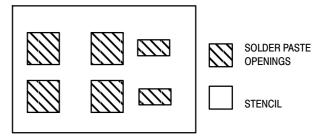

Prior to placing surface mount components onto a printed circuit board, solder paste must be applied to the pads. Solder stencils are used to screen the optimum amount. These stencils are typically 0.008 inches thick and may be made of brass or stainless steel. For packages such as the SC-59, SC-70/SOT-323, SOD-123, SOT-23, SOT-143, SOT-223, SO-8, SO-14, SO-16, and SMB/SMC diode packages, the stencil opening should be the same as the pad size or a 1:1 registration. This is not the case with the DPAK and D2PAK packages. If a 1:1 opening is used to screen solder onto the drain pad, misalignment and/or "tombstoning" may occur due to an excess of solder. For these two packages, the opening in the stencil for the paste should be approximately 50% of the tab area. The opening for the leads is still a 1:1 registration. Figure 4 shows a typical stencil for the DPAK and D2PAK packages. The

pattern of the opening in the stencil for the drain pad is not critical as long as it allows approximately 50% of the pad to be covered with paste.

Figure 4. Typical Stencil for DPAK and D2PAK Packages

### **SOLDERING PRECAUTIONS**

The melting temperature of solder is higher than the rated temperature of the device. When the entire device is heated to a high temperature, failure to complete soldering within a short time could result in device failure. Therefore, the following items should always be observed in order to minimize the thermal stress to which the devices are subjected.

- Always preheat the device.

- The delta temperature between the preheat and soldering should be 100°C or less.\*

- When preheating and soldering, the temperature of the leads and the case must not exceed the maximum temperature ratings as shown on the data sheet. When using infrared heating with the reflow soldering method, the difference should be a maximum of 10°C.

- The soldering temperature and time should not exceed 260°C for more than 10 seconds.

- When shifting from preheating to soldering, the maximum temperature gradient shall be 5°C or less.

- After soldering has been completed, the device should be allowed to cool naturally for at least three minutes.

Gradual cooling should be used since the use of forced cooling will increase the temperature gradient and will result in latent failure due to mechanical stress.

- Mechanical stress or shock should not be applied during cooling.

- \* Soldering a device without preheating can cause excessive thermal shock and stress which can result in damage to the device.

- \* Due to shadowing and the inability to set the wave height to incorporate other surface mount components, the D<sup>2</sup>PAK is not recommended for wave soldering.

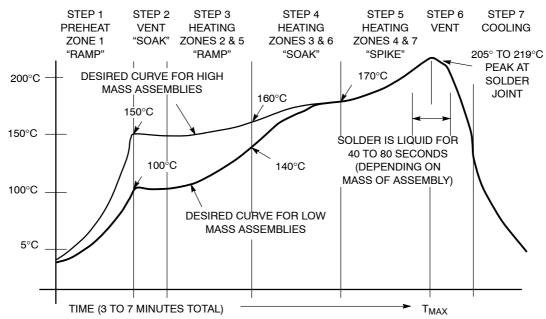

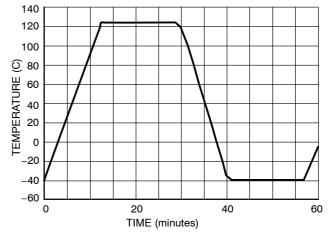

### TYPICAL SOLDER HEATING PROFILE

For any given circuit board, there will be a group of control settings that will give the desired heat pattern. The operator must set temperatures for several heating zones and a figure for belt speed. Taken together, these control settings make up a heating "profile" for that particular circuit board. On machines controlled by a computer, the computer remembers these profiles from one operating session to the next. Figure 5 shows a typical heating profile for use when soldering a surface mount device to a printed circuit board. This profile will vary among soldering systems, but it is a good starting point. Factors that can affect the profile include the type of soldering system in use, density and types of components on the board, type of solder used, and the type of board or substrate material being used. This profile shows temperature versus time. The line on the graph shows the

actual temperature that might be experienced on the surface of a test board at or near a central solder joint. The two profiles are based on a high density and a low density board. The Vitronics SMD310 convection/infrared reflow soldering system was used to generate this profile. The type of solder used was 62/36/2 Tin Lead Silver with a melting point between 177–189°C. When this type of furnace is used for solder reflow work, the circuit boards and solder joints tend to heat first. The components on the board are then heated by conduction. The circuit board, because it has a large surface area, absorbs the thermal energy more efficiently, then distributes this energy to the components. Because of this effect, the main body of a component may be up to 30 degrees cooler than the adjacent solder joints.

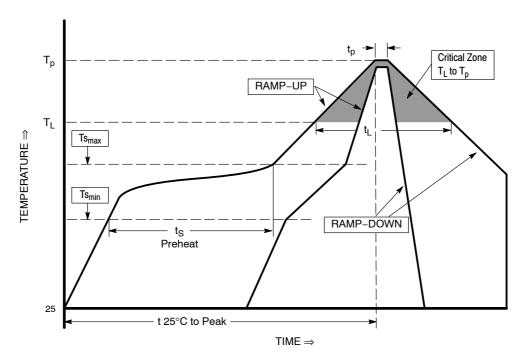

Figure 5. Typical Tin Lead (SnPb) Solder Heating Profile

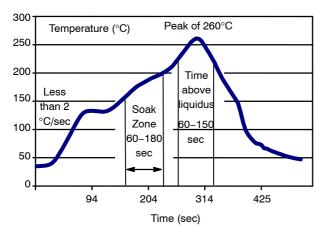

Figure 6. Typical Pb-Free Solder Heating Profile

| Profile Feature                                                                                                                  | Pb-Free Assembly                 |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Average Ramp-Up Rate (Ts <sub>max</sub> to Tp)                                                                                   | 3°C/second max                   |

| Preheat Temperature Min (Ts <sub>min</sub> ) Temperature Max (Ts <sub>max</sub> ) Time (ts <sub>min</sub> to ts <sub>max</sub> ) | 150°C<br>200°C<br>60–180 seconds |

| Time maintained above Temperature (T <sub>T</sub> ) Time (t <sub>T</sub> )                                                       | 217°C<br>60-150 seconds          |

| Peak Classification Temperature (Tp)                                                                                             | 260°C +5/-0                      |

| Time within 5°C of actual Peak Temperature (tp)                                                                                  | 20-40 seconds                    |

| Ramp-Down Rate                                                                                                                   | 6°C/second max                   |

| Time 25°C to Peak Temperature                                                                                                    | 8 minutes max                    |

# **Footprints for Soldering**

## **AND8211/D**

# Board Level Application Notes for DFN and QFN Packages

Prepared by: Steve St. Germain ON Semiconductor

ON Semiconductor®

http://onsemi.com

### **APPLICATION NOTE**

### INTRODUCTION

Various ON Semiconductor components are packaged in an advanced Dual or Quad Flat-Pack No-Lead package (DFN/QFN). The DFN/QFN platform represents the latest in surface mount packaging technology, it is important that the design of the Mounting Pads of the Printed Circuit Board (PCB), Soldermask and Stencil pattern, along with the assembly process, all follow the suggested guidelines outlined in this document.

### **DFN/QFN Package Overview**

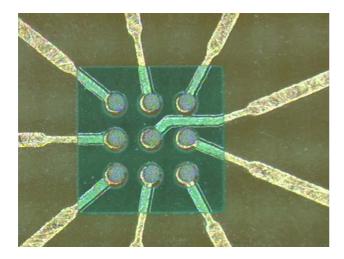

The DFN/QFN platform offers a versatility which allows either a single or multiple semiconductor devices to be connected together within a leadless package. This packaging flexibility is illustrated in Figure 7 where four devices are packaged together with a custom pad configuration.

Figure 7. The Underside of a 4-Chip 16 Pin DFN Package

Figure 8 illustrates a single site DFN semiconductor device package which allows for a large device.

Figure 8. The Underside of a Single-Chip 10 Pin DFN Package

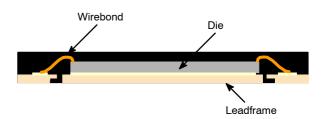

Figure 9. Cross-Section of a Single-Chip DFN Package

Figure 9 illustrates how the package height is reduced to a minimum by having both the die and wirebond pads on the same plane. When mounted, the leads are directly attached to the board without a space-consuming standoff, which is inherent in a leaded package.

Figure 9 also illustrates how the ends of the leads are flush with the edge of the package. This configuration allows for the maximum die size within a given footprint, while maximizing the board space efficiency.

In addition to these features, the DFN/QFN package has excellent thermal dissipation and reduced electrical parasitics due to its efficient and compact design.

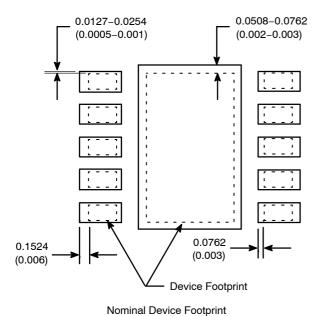

# Printed Circuit Board Solder Pad Design Guidelines

Refer to the case outline (specification sheet) drawing for the specific DFN/QFN package to be mounted. Based on the nominal package footprint dimensions from the case drawing. The PCB mounting pads need to be larger than the nominal package footprint (see Figure 10).

Note: On the occasion that there is not enough room to grow the PCB mounting pads per these guidelines, the recommendation would be to come as close to these guidelines as possible.

Figure 10. 10 Pin DFN Package Footprint Shown with PCB Mounting Pads

and PCB Mounting Pads

# Printed Circuit Board Solder Mask Design Guidelines

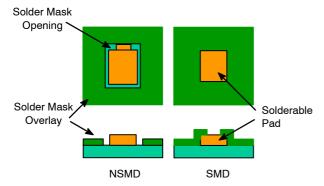

### **SMD and NSMD Pad Configurations**

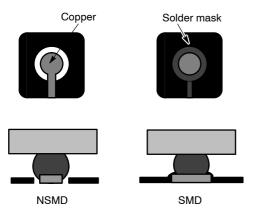

There are two different types of PCB pad configurations commonly used for surface mount leadless DFN/QFN style packages. The different configurations are:

- 1. Non Solder Masked Defined (NSMD)

- 2. Solder Masked Defined (SMD)

Figure 11. Comparison of NSMD vs. SMD Pads

As their titles describe, the NSMD contact pads have the solder mask pulled away from the solderable metallization, while the SMD pads have the solder mask over the edge of the metallization, as shown in Figure 11. With the SMD Pads, the solder mask restricts the flow of solder paste on the top of the metallization which prevents the solder from flowing along the side of the metal pad. This is different from the NSMD configuration where the solder will flow around both the top and the sides of the metallization.

Typically, the NSMD pads are preferred over the SMD configuration since defining the location and size of the copper pad is easier to control than the solder mask. This is based on the fact that the copper etching process is capable of a tighter tolerance than the solder masking process. This also allows for visual inspection of solder fillet.

In addition, the SMD pads will inherently create a stress concentration point where the solder wets to the pad on top of the lead. This stress concentration point is reduced when the solder is allowed to flow down the sides of the leads in the NSMD configuration.

# Printed Circuit Board Solder Mask Design Guidelines

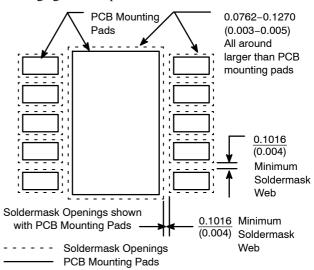

When dimensionally possible, the solder mask should be located within a range of 0.0762–0.1270 mm (0.003–0.005 in) away from the edge of the PCB mounting pad (see Figure 12). This spacing is used to compensate for the registration tolerances of the solder mask, as well as to insure that the solder is not inhibited by the mask as it reflows along the sides of the metal pad.

The solder mask web (between openings) is the controlling factor in the pattern, and needs to be held to a minimum of 0.1016 mm (0.004 in). This minimum is the current PCB suppliers standard minimum web for manufacturability. Because of this web restriction, solder mask openings around PCB pads may need to be less than the recommended shown. Whenever possible, keeping to the range given will provide for the best results.

Figure 12. Typical DFN Package – PCB Mounting Pads Shown with Soldermask Openings

### **DFN/QFN Board Mounting Process**

The DFN/QFN board mounting process is optimized by first defining and controlling the following.

- 1. Solderable metallization on the PCB contacts.

- 2. Choice of proper solder paste.

- 3. Solder paste on the PCB.

- 4. Package placement.

- 5. Reflow of the solder paste.

- 6. Final solder joint inspection.

Recommendations for each of these processes are located below.

### **PCB Solderable Metallization**

There are currently three common solderable coatings which are used for PCB surface mount devices. In any case, it is imperative that the coating is uniform, conforming, and free of impurities to insure a consistant solderable system.

The first coating consists of an Organic Solderability Protectant (OSP) applied over the bare copper feature. OSP coating assists in reducing oxidation in order to preserve the copper metallization for soldering. It allows for multiple passes through reflow ovens without degradation of the solderability. The OSP coating is dissolved by the flux when the solder paste is applied to the metal features. Coating thickness recommended by OSP manufacturers is between 0.25 and 0.35 microns.

The second coating is a metalized coating which consists of plated electroless nickel over the copper pad, followed by a coat of immersion gold. The thickness of the electroless nickel layer is determined by the allowable internal material stresses and the temperature excursions the board will be subjected to throughout its lifetime. Even though the gold metallization is typically a self-limiting process, the thickness should be at least  $0.05~\mu m$  thick, and not consist of more than 5% of the overall solder volume. Having excessive gold in the solder joint can create gold embitterment which may affect the reliability of the joint.

The third is a tin-lead coating, commonly called Hot Air Solder Level (HASL). This type of PCB pad finish is not recommended for DFN/QFN type packages. The major issue is the inability to consistently control the amount of solder coating applied to each pad. This results in dome-shaped pads of various heights. As the industry drives for finer and finer pitch, solder bridging becomes a common problem between mounting pads.

### Solder Type

Solder paste such as Cookson Electronics' WS3060 with a Type 3 or smaller sphere size is recommended. The WS3060 has a water-soluble flux for cleaning. Cookson Electronics' PNC0106A can be used if a no-clean flux is preferred.

### Solder Screening onto the PCB

Stencil screening the solder paste onto the PCB is commonly used in the industry. The recommended stencil thickness used is 0.075~mm to 0.127~mm (0.003~in to 0.005~in). The sidewalls of the stencil openings should be tapered approximately  $5^{\circ}$  to facilitate the release of the paste when the stencil is removed from the PCB.

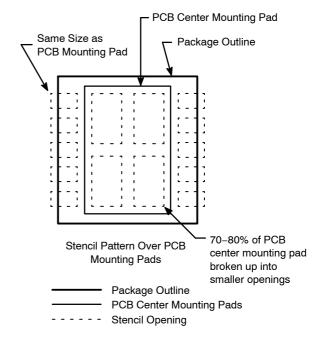

The stencil opening should be the same size as the PCB mounting pad. The exception is when there is a large center flag on the device. Then the stencil opening should allow for 70–80% coverage of the PCB mounting pad. This opening should also be divided into smaller cavities to aid in the flow of solder during the reflow process (see Figure 13). Dividing the larger die pads into smaller screen openings reduces the risk of solder voiding and allows the solder joints for the smaller terminal pads to be at the same height as the larger ones.

Figure 13. Typical DFN Package with Stencil Openings Shown Over PCB Mounting Pads

### Package Placement onto the PCB

Pick and place equipment with the standard tolerance of  $\pm 0.05$  mm (0.002 in) or better is recommended. The package will tend to center itself and correct for slight placement errors during the reflow process due to the surface tension of the solder.

### **Solder Reflow**

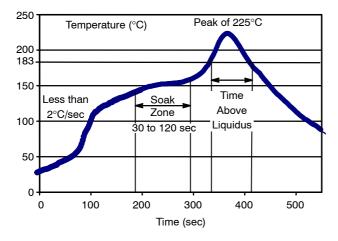

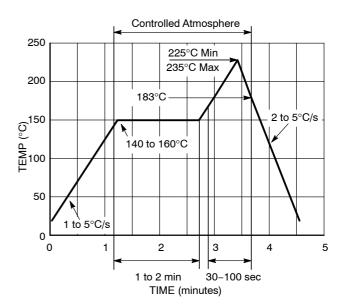

Once the package is placed on the PC board along with the solder paste, a standard surface mount reflow process can be used to mount the part. Figures 14 and 15 are examples of standard reflow profiles for standard eutectic and lead free solder alloys.

### **SOLDERRM**

The exact profile will be determined, and is available, by the manufacture of the paste since the chemistry and viscosity of the flux matrix will vary. These variations will require small changes in the profile in order to achieve an optimized process.

Figure 14. Typical Reflow Profile for Eutectic Tin/Lead Solder

Figure 15. Typical Reflow Profile for Pb-Free Solder

In general, the temperature of the part should be raised not more than 2°C/sec during the initial stages of the reflow profile. The soak zone then occurs when the part is approximately 150°C and should last for 60 to 180 seconds for Pb–free profiles (30–120 sec for Eutectic profiles). Typically, extending the time in the soak zone will reduce the risk of voiding within the solder. The temperature is then raised and will be above the liquidus of the solder for 60 to 150 seconds for Pb–free profiles (30–100 sec for Eutectic profiles) depending on the mass of the board. The peak temperature of the profile should be between 245 and 260°C for Pb–free solder alloys (205–225°C) for eutectic solders.

If required, removal of the residual solder flux can be completed by using the recommended procedures set forth by the flux manufacturer.

### **Final Solder Inspection**

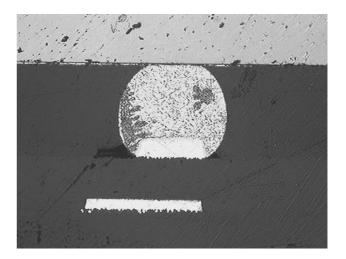

The inspection of the solder joints is commonly performed with the use of an X-ray inspection system. With this tool, one can locate defects such as shorts between pads, open contacts, voids within the solder as well as any extraneous solder.

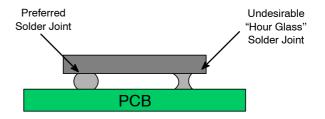

In addition to searching for defects, the mounted device should be rotated on its side to inspect the sides of the solder joints with an X-ray inspection system. The solder joints should have enough solder volume with the proper stand-off height so that an "Hour Glass" shaped connection is not formed as shown below in Figure 16. "Hour Glass" solder joints are a reliability concern and must be avoided.

Figure 16. Side View of DFN Illustrating Preferred and Undesirable Solder Joints

### **Rework Procedure**

Due to the fact that the DFN/QFN's are leadless devices, the entire package must be removed from the PC board if there is an issue with the solder joints. It is important to minimize the chance of overheating neighboring devices during the removal of the package since the devices are typically in close proximity with each other.

Standard SMT rework systems are recommended for this procedure since the airflow and temperature gradients can be carefully controlled. It is also recommend that the PC board be placed in an oven at 125°C for four to eight hours prior to heating the parts to remove excess moisture from the packages. In order to control the region which will be exposed to reflow temperatures, the board should be heated to a 100°C by conduction through the backside of the board in the location of the device. Typically, heating nozzles are then used to increase the temperature locally.

Once the device's solder joints are heated above their liquidus temperature, the package is quickly removed and the pads on the PC board are cleaned. The cleaning of the pads is typically performed with a blade–style conductive tool with a desoldering braid. A no clean flux is used during this process in order to simplify the procedure.

### **SOLDERRM**

Solder paste is then deposited or screened onto the site in preparation of mounting a new device. Due to the close proximity of the neighboring packages in most PC board configurations, a miniature stencil for the individual component is typically required. The same stencil design that was originally used to mount the package can be applied to the mini-stencil for redressing the pads.

Due to the small pad configurations of the DFN/QFN, and since the pads are on the underside of the package, a manual pick and place procedure without the aid of magnification is not recommended. A dual image optical system where the underside of the package can be aligned to the PC board should be used instead.

Reflowing the component onto the board can be accomplished by either passing the board through the original reflow profile, or by selectively heating the package with the same process that was used to remove it. The benefit with subjecting the entire board to a second reflow is that the new part will be mounted consistently and by a profile that is already defined. The disadvantage is that all of the other devices mounted with the same solder type will be reflowed for a second time. If subjecting all of the parts to a second reflow is either a concern or unacceptable for a specific application, than the localized reflow option would be the recommended procedure.

# **AN1040/D**

# **Mounting Considerations for Power Semiconductors**

Prepared by: Bill Roehr

# ON

### **ON Semiconductor**

http://onsemi.com

### **APPLICATION NOTE**

### INTRODUCTION

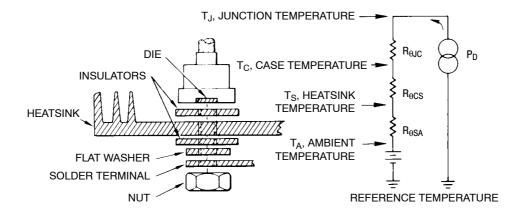

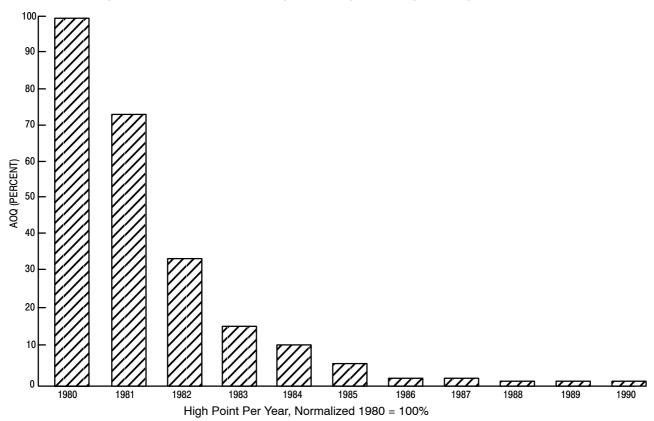

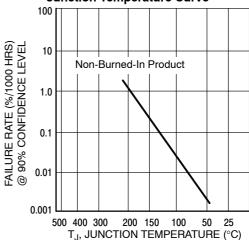

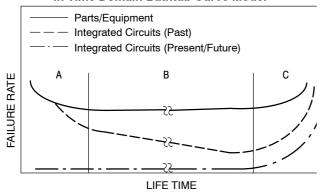

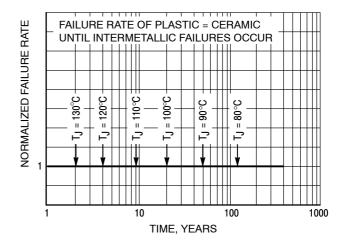

Current and power ratings of semiconductors are inseparably linked to their thermal environment. Except for lead-mounted parts used at low currents, a heat exchanger is required to prevent the junction temperature from exceeding its rated limit, thereby running the risk of a high failure rate. Furthermore, the semiconductor industry's field history indicated that the failure rate of most silicon semiconductors decreases approximately by one-half for a decrease in junction temperature from 160°C to 135°C. (1) Guidelines for designers of military power supplies impose a 110°C limit upon junction temperature. (2) Proper mounting minimizes the temperature gradient between the semiconductor case and the heat exchanger.

Most early life field failures of power semiconductors can be traced to faulty mounting procedures. With metal packaged devices, faulty mounting generally causes unnecessarily high junction temperature, resulting in reduced component lifetime, although mechanical damage has occurred on occasion from improperly mounting to a warped surface. With the widespread use of various plastic–packaged semiconductors, the prospect of mechanical damage is very significant. Mechanical damage can impair the case moisture resistance or crack the semiconductor die.

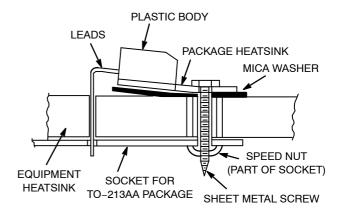

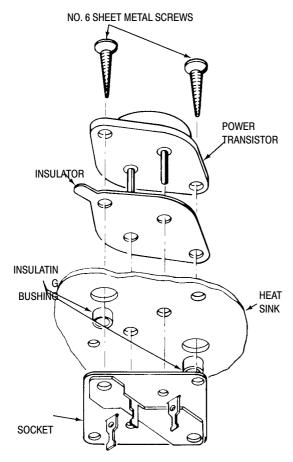

Figure 17 shows an example of doing nearly everything wrong. A tab mount TO-220 package is shown being used as a replacement for a TO-213AA (TO-66) part which was socket mounted. To use the socket, the leads are bent - an operation which, if not properly done, can crack the package, break the internal bonding wires, or crack the die. The package is fastened with a sheet-metal screw through a 1/4" hole containing a fiber-insulating sleeve. The force used to tighten the screw tends to pull the package into the hole, possibly causing enough distortion to crack the die. In addition the contact area is small because of the area consumed by the large hole and the bowing of the package; the result is a much higher junction temperature than expected. If a rough heatsink surface and/or burrs around the hole were displayed in the illustration, most but not all poor mounting practices would be covered.

Figure 17. Extreme Case of Improperly Mounting a Semiconductor (Distortion Exaggerated)

In many situations the case of the semiconductor must be electrically isolated from its mounting surface. The isolation material is, to some extent, a thermal isolator as well, which raises junction operating temperatures. In addition, the possibility of arc-over problems is introduced if high voltages are present. Various regulating agencies also impose creepage distance specifications which further complicates design. Electrical isolation thus places additional demands upon the mounting procedure.

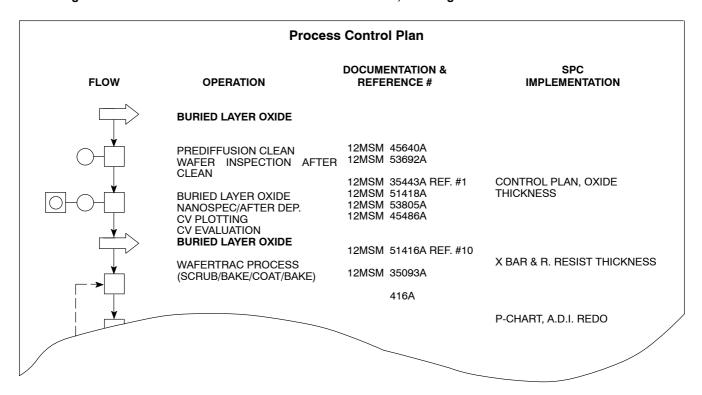

Proper mounting procedures usually necessitate orderly attention to the following:

- 1. Preparing the mounting surface

- 2. Applying a thermal grease (if required)

- 3. Installing the insulator (if electrical isolation is desired)

- 4. Fastening the assembly

- 5. Connecting the terminals to the circuit

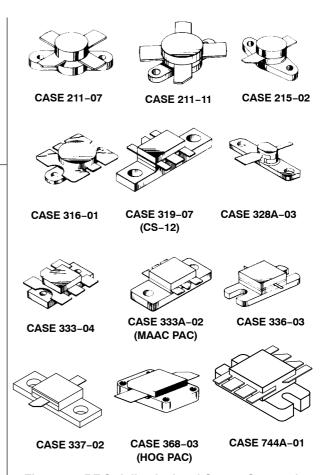

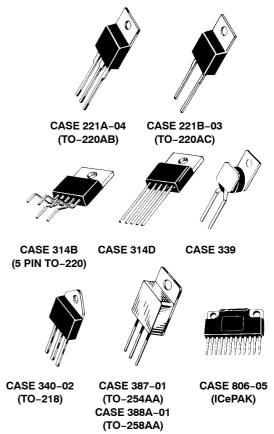

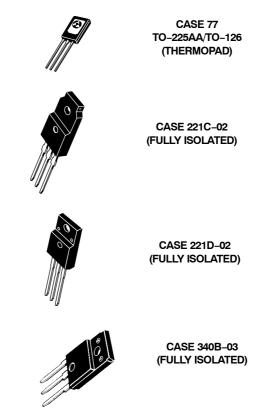

In this note, mounting procedures are discussed in general terms for several generic classes of packages. As newer packages are developed, it is probable that they will fit into the generic classes discussed in this note. Unique requirements are given on data sheets pertaining to the particular package. The following classes are defined:

Stud Mount

Flange Mount

Pressfit

Plastic Body Mount

Tab Mount

Surface Mount

Appendix A contains a brief review of thermal resistance concepts. Appendix B discusses measurement difficulties with interface thermal resistance tests. Appendix C indicates the type of accessories supplied by a number of manufacturers.

### MOUNTING SURFACE PREPARATION

In general, the heatsink mounting surface should have a flatness and finish comparable to that of the semiconductor package. In lower power applications, the heatsink surface is satisfactory if it appears flat against a straight edge and is free from deep scratches. In high-power applications, a more detailed examination of the surface is required. Mounting holes and surface treatment must also be considered.

### **Surface Flatness**

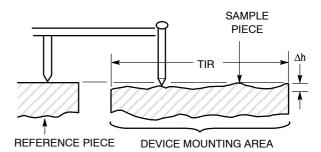

Surface flatness is determined by comparing the variance in height ( $\Delta h$ ) of the test specimen to that of a reference standard as indicated in Figure 18. Flatness is normally specified as a fraction of the Total Indicator Reading (TIR). The mounting surface flatness, i.e.,  $\Delta h/TIR$ , if less than 4 mils per inch, normal for extruded aluminum, is satisfactory in most cases.

### **Surface Finish**

Surface finish is the average of the deviations both above and below the mean value of surface height. For minimum interface resistance, a finish in the range of 50 to 60 microinches is satisfactory; a finer finish is costly to achieve and does not significantly lower contact resistance. Tests conducted by Thermalloy, Inc., using a copper TO–204 (TO–3) package with a typical 32-microinch finish, showed that heatsink finishes between 16 and 64  $\mu$ -in caused less than  $\pm 2.5\%$  difference in interface thermal resistance when the voids and scratches were filled with a thermal joint compound. (3) Most commercially available cast or extruded heatsinks will require spotfacing when used in high-power applications. In general, milled or machined surfaces are satisfactory if prepared with tools in good working condition.

### **Mounting Holes**

Mounting holes generally should only be large enough to allow clearance of the fastener. The larger thick flange type packages having mounting holes removed from the semiconductor die location, such as the TO-3, may successfully be used with larger holes to accommodate an insulating bushing, but many plastic encapsulated packages are intolerant of this condition. For these packages, a smaller screw size must be used such that the hole for the bushing does not exceed the hole in the package.

Punched mounting holes have been a source of trouble because if not properly done, the area around a punched hole is depressed in the process. This "crater" in the heatsink around the mounting hole can cause two problems. The device can be damaged by distortion of the package as the mounting pressure attempts to conform it to the shape of the heatsink indentation, or the device may only bridge the crater and leave a significant percentage of its heat–dissipating surface out of contact with the heatsink. The first effect may often be detected immediately by visual cracks in the package (if plastic), but usually an unnatural stress is imposed, which results in an early–life failure. The second effect results in hotter operation and is not manifested until much later.

Although punched holes are seldom acceptable in the relatively thick material used for extruded aluminum heatsinks, several manufacturers are capable of properly utilizing the capabilities inherent in both fine-edge blanking or sheared-through holes when applied to sheet metal as commonly used for stamped heatsinks. The holes are pierced using Class A progressive dies mounted on four-post die sets equipped with proper pressure pads and holding fixtures.

TIR = TOTAL INDICATOR READING

Figure 18. Surface Flatness Measurement

### **SOLDERRM**

When mounting holes are drilled, a general practice with extruded aluminum, surface cleanup is important. Chamfers must be avoided because they reduce heat transfer surface and increase mounting stress. However, the edges must be broken to remove burrs which cause poor contact between device and heatsink and may puncture isolation material.

### **Surface Treatment**

Many aluminum heatsinks are black-anodized to improve radiation ability and prevent corrosion. Anodizing results in significant electrical but negligible thermal insulation. It need only be removed from the mounting area when electrical contact is required. Heatsinks are also available which have a nickel plated copper insert under the semiconductor mounting area. No treatment of this surface is necessary.

Another treated aluminum finish is iridite, or chromateacid dip, which offers low resistance because of its thin surface, yet has good electrical properties because it resists oxidation. It need only be cleaned of the oils and films that collect in the manufacture and storage of the sinks, a practice which should be applied to all heatsinks.

For economy, paint is sometimes used for sinks; removal of the paint where the semiconductor is attached is usually required because of paint's high thermal resistance. However, when it is necessary to insulate the semiconductor package from the heatsink, hard anodized or painted surfaces allow an easy installation for low voltage applications. Some manufacturers will provide anodized or painted surfaces meeting specific insulation voltage requirements, usually up to 400 volts.

It is also necessary that the surface be free from all foreign material, film, and oxide (freshly bared aluminum forms an oxide layer in a few seconds). Immediately prior to assembly, it is a good practice to polish the mounting area with No. 000 steel wool, followed by an acetone or alcohol rinse.

### INTERFACE DECISIONS

When any significant amount of power is being dissipated, something must be done to fill the air voids between mating surfaces in the thermal path. Otherwise the interface thermal resistance will be unnecessarily high and quite dependent upon the surface finishes.

For several years, thermal joint compounds, often called grease, have been used in the interface. They have a resistivity of approximately 60°C/W/in whereas air has 1200°C/W/in. Since surfaces are highly pock–marked with minute voids, use of a compound makes a significant reduction in the interface thermal resistance of the joint. However, the grease causes a number of problems, as discussed in the following section.

To avoid using grease, manufacturers have developed dry conductive and insulating pads to replace the more traditional materials. These pads are conformal and therefore partially fill voids when under pressure.

### Thermal Compounds (Grease)

Joint compounds are a formulation of fine zinc or other conductive particles in a silicone oil or other synthetic base fluid which maintains a grease-like consistency with time and temperature. Since some of these compounds do not spread well, they should be evenly applied in a very thin layer using a spatula or lintless brush, and wiped lightly to remove excess material. Some cyclic rotation of the package will help the compound spread evenly over the entire contact area. Some experimentation is necessary to determine the correct quantity; too little will not fill all the voids, while too much may permit some compound to remain between well mated metal surfaces where it will substantially increase the thermal resistance of the joint.

To determine the correct amount, several semiconductor samples and heatsinks should be assembled with different amounts of grease applied evenly to one side of each mating surface. When the amount is correct a very small amount of grease should appear around the perimeter of each mating surface as the assembly is slowly torqued to the recommended value. Examination of a dismantled assembly should reveal even wetting across each mating surface. In production, assemblers should be trained to slowly apply the specified torque even though an excessive amount of grease appears at the edges of mating surfaces. Insufficient torque causes a significant increase in the thermal resistance of the interface.

To prevent accumulation of airborne particulate matter, excess compound should be wiped away using a cloth moistened with acetone or alcohol. These solvents should not contact plastic–encapsulated devices, as they may enter the package and cause a leakage path or carry in substances which might attack the semiconductor chip.

The silicone oil used in most greases has been found to evaporate from hot surfaces with time and become deposited on other cooler surfaces. Consequently, manufacturers must determine whether a microscopically thin coating of silicone oil on the entire assembly will pose any problems. It may be necessary to enclose components using grease. The newer synthetic base greases show far less tendency to migrate or creep than those made with a silicone oil base. However, their currently observed working temperature range are less, they are slightly poorer on thermal conductivity and dielectric strength and their cost is higher.

Data showing the effect of compounds on several package types under different mounting conditions is shown in Figure 1. The rougher the surface, the more valuable the grease becomes in lowering contact resistance; therefore, when mica insulating washers are used, use of grease is generally mandatory. The joint compound also improves the breakdown rating of the insulator.

#### **Conductive Pads**

Because of the difficulty of assembly using grease and the evaporation problem, some equipment manufacturers will not, or cannot, use grease. To minimize the need for grease, several vendors offer dry conductive pads which approximate performance obtained with grease. Data for a greased bare joint and a joint using Grafoil®, a dry graphite compound, is shown in the data of Figure 19 through Figure 22. Grafoil is claimed to be a replacement for grease when no electrical isolation is required; the data indicates it does indeed perform as well as grease. Another conductive pad available from Aavid is called Kon−Dux™. It is made with a unique, grain oriented, flake−like structure (patent pending). Highly compressible, it becomes formed to the surface roughness of both the heatsink and semiconductor. Manufacturer's data shows it to provide an interface thermal resistance better than a metal interface with filled silicone grease. Similar dry conductive pads are available from other manufacturers. They are a fairly recent development; long term problems, if they exist, have not yet become evident.

Table 1. Approximate Values for Interface Thermal Resistance Data from Measurements Performed in ON Semiconductor Applications Engineering Laboratory

Dry interface values are subject to wide variation because of extreme dependence upon surface conditions.

Unless otherwise noted the case temperature is monitored by a thermocouple located directly under the die reached through a hole in the heatsink. (See Appendix B for a discussion of Interface Thermal Resistance Measurements.)

|                                |                           | Interface Thermal Resistance (°C/W) |      |       |                |       |               |             |

|--------------------------------|---------------------------|-------------------------------------|------|-------|----------------|-------|---------------|-------------|

| Package Type and Data          |                           | Metal-to-Metal                      |      | ,     | With Insulator |       |               |             |

| JEDEC<br>Outlines              | Description               | Test Torque<br>In-Lb                | Dry  | Lubed | Dry            | Lubed | Туре          | See<br>Note |

| DO-203AA, TO-210AA<br>TO-208AB | 10-32 Stud<br>7/16" Hex   | 15                                  | 0.3  | 0.2   | 1.6            | 0.8   | 3 mil<br>Mica |             |

| DO-203AB, TO-210AC<br>TO-208   | 1/4-28 Stud<br>11/16" Hex | 25                                  | 0.2  | 0.1   | 0.8            | 0.6   | 5 mil<br>Mica |             |

| DO-208AA                       | Pressfit, 1/2"            | -                                   | 0.15 | 0.1   | -              | -     | -             |             |

| TO-204AA (TO-3)                | Diamond Flange            | 6                                   | 0.5  | 0.1   | 1.3            | 0.36  | 3 mil<br>Mica | 1           |

| TO-213AA (TO-66)               | Diamond Flange            | 6                                   | 1.5  | 0.5   | 2.3            | 0.9   | 2 mil<br>Mica |             |

| TO-126                         | Thermopad<br>1/4" x 3/8"  | 6                                   | 2.0  | 1.3   | 4.3            | 3.3   | 2 mil<br>Mica |             |

| TO-220AB                       | Thermowatt                | 8                                   | 1.2  | 1.0   | 3.4            | 1.6   | 2 mil<br>Mica | 1, 2        |

NOTES: 1. See Figure 19 through Figure 23 for additional data on TO-3 and TO-220 packages.

#### **INSULATION CONSIDERATIONS**

Since most power semiconductors use are vertical device construction it is common to manufacture power semiconductors with the output electrode (anode, collector or drain) electrically common to the case; the problem of isolating this terminal from ground is a common one. For lowest overall thermal resistance, which is quite important when high power must be dissipated, it is best to isolate the entire heatsink/semiconductor structure from ground, rather than to use an insulator between the semiconductor and the heatsink. Heatsink isolation is not always possible, however, because of EMI requirements, safety reasons, instances where a chassis serves as a heatsink or where a heatsink is common to several non isolated packages. In

these situations insulators are used to isolate the individual components from the heatsink. Newer packages, such as the ON Semiconductor FULLPAK™ and EMS modules, contain the electrical isolation material within, thereby saving the equipment manufacturer the burden of addressing the isolation problem.

#### **Insulator Thermal Resistance**

When an insulator is used, thermal grease is of greater importance than with a metal-to-metal contact, because two interfaces exist instead of one and some materials, such as mica, have a hard, markedly uneven surface. With many isolation materials reduction of interface thermal resistance of between 2 to 1 and 3 to 1 are typical when grease is used.

<sup>2.</sup> Screw not insulated. See Figure 36.

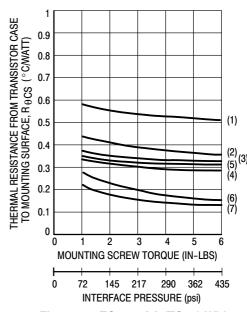

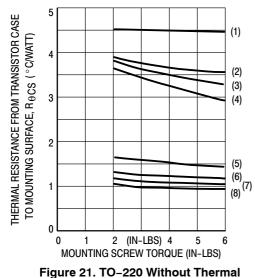

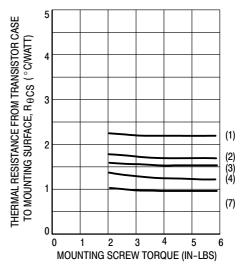

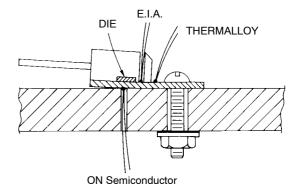

Data obtained by Thermalloy, showing interface resistance for different insulators and torques applied to TO-204 (TO-3) and TO-220 packages, are shown in Figure 19 through Figure 22, for bare and greased surfaces. Similar materials to those shown are available from several manufacturers. It is obvious that with some arrangements, the interface thermal resistance exceeds that of the semiconductor (junction to case).

Referring to Figure 19 through Figure 22, one may conclude that when high power is handled, beryllium oxide is unquestionably the best. However, it is an expensive choice. (It should not be cut or abraded, as the dust is

highly toxic.) Thermafilm<sup>™</sup> is a filled polymide material which is used for isolation (variation of Kapton®). It is a popular material for low power applications because of its low cost ability to withstand high temperatures, and ease of handling in contrast to mica which chips and flakes easily.

A number of other insulating materials are also shown. They cover a wide range of insulation resistance, thermal resistance and ease of handling. Mica has been widely used in the past because it offers high breakdown voltage and fairly low thermal resistance at a low cost but it certainly should be used with grease.

Figure 19. TO-204AA (TO-3) Without Thermal Grease

- (2) Mica, .003 (.08) thick.

- (3) Mica, .002 (.05) thick.

- (4) Hard anodized, .020 (.51) thick

- (5) Aluminum oxide, .062 (1.57) thick

- (6) Beryllium oxide, .062 (1.57) thick

- (7) Bare joint no finish.

- (8) Grafoil, .005 (.13) thick.\*

\*Grafoil is not an insulating material.

Figure 20. TO-204AA (TO-3) With Thermal Grease

- (1) Thermafilm, .002 (.05) thick.

- (2) Mica, .003 (.08) thick.

- (3) Mica, .002 (.05) thick.

- (4) **Hard anodized**, .020 (.51) thick.

- (5) **Thermasil II**, .009 (.23)

- (6) **Thermasil III**, .007'6 (.15)

- (7) Bare ioint no finish.

- (8) Grafoil, .005 (.13) thick.\*

- \*Grafoil is not an insulating material.

Figure 22. TO-220 With Thermal Grease

Grease G

Silicone rubber insulators have gained favor because they are somewhat conformal under pressure. Their ability to fill in most of the metal voids at the interface reduces the need for thermal grease. When first introduced, they suffered from cut-through after a few years in service. The ones presently available have solved this problem by having imbedded pads of Kapton or fiberglass. By comparing Figure 21 and Figure 22, it can be noted that Thermasil  $^{\text{TM}}$ , a filled silicone rubber, without grease, has about the same interface thermal resistance as greased mica for the TO-220 package.

A number of manufacturers offer silicone rubber insulators. Figure 2 shows measured performance of a number of these insulators under carefully controlled, nearly identical conditions. The interface thermal resistance extremes are over 2:1 for the various materials. It is also clear that some of the insulators are much more tolerant than others of out-of-flat surfaces. Since the tests were performed, newer products have been introduced. The Bergquist K-10® pad, for example, is described as having about 2/3 the interface resistance of the Sil Pad® 1000 which would place its performance close to the Chomerics 1671 pad. Aavid also offers an isolated pad called Rubber-Duc™, however it is only available vulcanized to a heatsink and therefore was not included in the comparison. Published data from Aavid shows  $R_{\theta CS}$ below 0.3°C/W for pressures above 500 psi. However, surface flatness and other details are not specified so a comparison cannot be made with other data in this note.

Table 2. Thermal Resistance of Silicone Rubber Pads

| Manufacturer     | Product         | R <sub>OCS</sub> @<br>3 Mils* | R <sub>θCS</sub> @<br>7.5 Mils* |

|------------------|-----------------|-------------------------------|---------------------------------|

| Wakefield        | Delta Pad 173-7 | .790                          | 1.175                           |

| Bergquist        | Sil Pad K-4®    | .752                          | 1.470                           |

| Stockwell Rubber | 1867            | .742                          | 1.015                           |

| Bergquist        | Sil Pad 400-9®  | .735                          | 1.205                           |

| Thermalloy       | Thermasil II    | .680                          | 1.045                           |

| Shin-Etsu        | TC-30AG         | .664                          | 1.260                           |

| Bergquist        | Sil Pad 400-7®  | .633                          | 1.060                           |

| Chomerics        | 1674            | .592                          | 1.190                           |

| Wakefield        | Delta Pad 174-9 | .574                          | .755                            |

| Bergquist        | Sil Pad 1000®   | .529                          | .935                            |

| Ablestik         | Thermal Wafers  | .500                          | .990                            |

| Thermalloy       | Thermasil III   | .440                          | 1.035                           |

| Chomerics        | 1671            | .367                          | .655                            |

<sup>\*</sup>Test Fixture Deviation from flat from Thermalloy EIR86-1010.

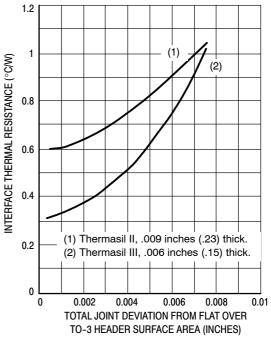

The thermal resistance of some silicone rubber insulators is sensitive to surface flatness when used under a fairly rigid base package. Data for a TO-204AA (TO-3) package insulated with Thermasil is shown on Figure 23. Observe that the "worst case" encountered (7.5 mils) yields results having about twice the thermal resistance of the "typical case" (3 mils), for the more conductive insulator. In order for Thermasil III to exceed the performance of greased

mica, total surface flatness must be under 2 mils, a situation that requires spot finishing.

Data courtesy of Thermalloy

Figure 23. Effect of Total Surface Flatness on Interface Resistance Using Silicon Rubber Insulators

Silicon rubber insulators have a number of unusual characteristics. Besides being affected by surface flatness and initial contact pressure, time is a factor. For example, in a study of the Cho–Therm® 1688 pad thermal interface impedance dropped from 0.90°C/W to 0.70°C/W at the end of 1000 hours. Most of the change occurred during the first 200 hours where  $R_{\theta CS}$  measured 0.74°C/W. The torque on the conventional mounting hardware had decreased to 3 in–lb from an initial 6 in–lb. With nonconformal materials, a reduction in torque would have increased the interface thermal resistance.

Because of the difficulties in controlling all variables affecting tests of interface thermal resistance, data from different manufacturers is not in good agreement. Figure 3 shows data obtained from two sources. The relative performance is the same, except for mica which varies widely in thickness. Appendix B discusses the variables which need to be controlled. At the time of this writing ASTM Committee D9 is developing a standard for interface measurements.

The conclusions to be drawn from all this data is that some types of silicon rubber pads, mounted dry, will out perform the commonly used mica with grease. Cost may be a determining factor in making a selection.

Table 3. Performance of Silicon Rubber Insulators

Tested Per MIL-I-49456

|                       | Measured Thermal Resistance (°C/W) |                                  |  |  |  |

|-----------------------|------------------------------------|----------------------------------|--|--|--|

| Material              | Thermalloy<br>Data <sup>(1)</sup>  | Bergquist<br>Data <sup>(2)</sup> |  |  |  |

| Bare Joint, greased   | 0.033                              | 0.008                            |  |  |  |

| BeO, greased          | 0.082                              | -                                |  |  |  |

| Cho-Therm, 1617       | 0.233                              | -                                |  |  |  |

| Q Pad (non-insulated) | _                                  | 0.009                            |  |  |  |

| Sil Pad, K-10         | 0.263                              | 0.200                            |  |  |  |

| Thermasil III         | 0.267                              | -                                |  |  |  |

| Mica, greased         | 0.329                              | 0.400                            |  |  |  |

| Sil Pad 1000          | 0.400                              | 0.300                            |  |  |  |

| Cho-Therm 1674        | 0.433                              | _                                |  |  |  |

| Thermasil II          | 0.500                              | _                                |  |  |  |

| Sil Pad 400           | 0.533                              | 0.440                            |  |  |  |

| Sil Pad K-4           | 0.583                              | 0.440                            |  |  |  |

- (1) From Thermalloy EIR 87-1030

- (2) From Bergquist Data Sheet

#### **Insulation Resistance**

When using insulators, care must be taken to keep the mating surfaces clean. Small particles of foreign matter can puncture the insulation, rendering it useless or seriously lowering its dielectric strength. In addition, particularly when voltages higher than 300 V are encountered, problems with creepage may occur. Dust and other foreign material can shorten creepage distances significantly; so having a clean assembly area is important. Surface roughness and humidity also lower insulation resistance. Use of thermal grease usually raises the withstand voltage of the insulation system but excess must be removed to avoid collecting dust. Because of these factors, which are not amenable to analysis, hi–pot testing should be done on prototypes and a large margin of safety employed.

### **Insulated Electrode Packages**

Because of the nuisance of handling and installing the accessories needed for an insulated semiconductor mounting, equipment manufacturers have longed for cost-effective insulated packages since the 1950's. The first to appear were stud mount types which usually have a layer of beryllium oxide between the stud hex and the can. Although effective, the assembly is costly and requires manual mounting and lead wire soldering to terminals on top of the case. In the late eighties, a number of electrically became available isolated parts from semiconductor manufacturers. These offerings presently consist of multiple chips and integrated circuits as well as the more conventional single chip devices.

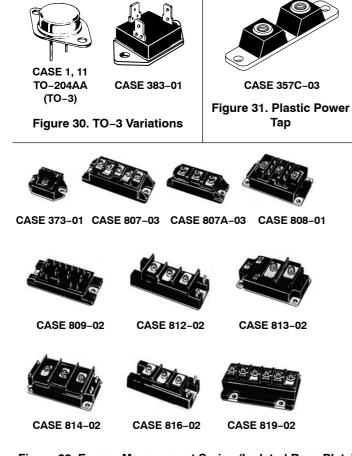

The newer insulated packages can be grouped into two categories. The first has insulation between the semiconductor chips and the mounting base; an exposed area of the mounting base is used to secure the part. The EMS (Energy Management Series) Modules, shown on Figure 32, Case 806 (ICePAK™) and Case 388A (TO-258AA) (see Figure 32) are examples of parts in this category. The second category contains parts which have a plastic overmold covering the metal mounting base. The isolated, Case 221C, illustrated in Figure 37, is an example of parts in the second category.

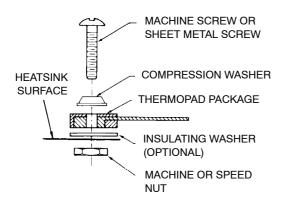

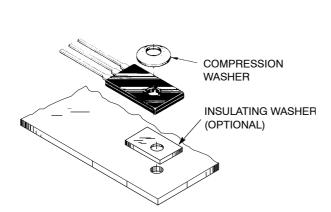

Parts in the first category – those with an exposed metal flange or tab – are mounted the same as their non–insulated counterparts. However, as with any mounting system where pressure is bearing on plastic, the overmolded type should be used with a conical compression washer, described later in this note.

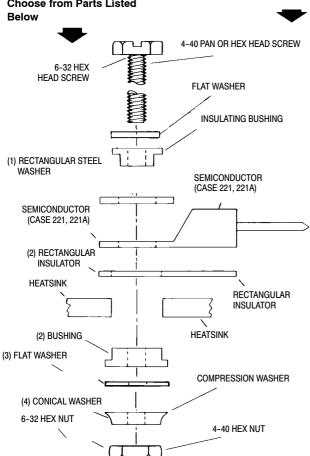

# FASTENER AND HARDWARE CHARACTERISTICS

Characteristics of fasteners, associated hardware, and the tools to secure them determine their suitability for use in mounting the various packages. Since many problems have arisen because of improper choices, the basic characteristics of several types of hardware are discussed next.

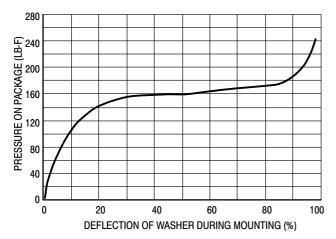

#### **Compression Hardware**

Normal split ring lock washers are not the best choice for mounting power semiconductors. A typical #6 washer flattens at about 50 pounds, whereas 150 to 300 pounds is needed for good heat transfer at the interface. A very useful piece of hardware is the conical, sometimes called a Belleville washer, compression washer. As shown in Figure 24, it has the ability to maintain a fairly constant pressure over a wide range of its physical deflection generally 20% to 80%. When installing, the assembler applies torque until the washer depresses to half its original height. (Tests should be run prior to setting up the assembly line to determine the proper torque for the fastener used to achieve 50% deflection.) The washer will absorb any cyclic expansion of the package, insulating washer or other materials caused by temperature changes. Conical washers are the key to successful mounting of devices requiring strict control of the mounting force or when plastic hardware is used in the mounting scheme. They are used with the large face contacting the packages. A new variation of the conical washer includes it as part of a nut assembly. Called a "sync nut," the patented device can be soldered to a PC board and the semiconductor mounted with a 6-32 machine screw. (4)

Figure 24. Characteristics of the Conical Compression Washers Designed for Use with Plastic Body Mounted Semiconductors

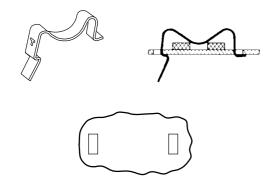

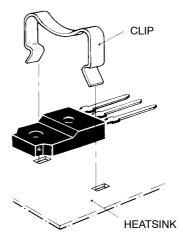

#### Clips

Fast assembly is accomplished with clips. When only a few watts are being dissipated, the small board-mounted or free-standing heat dissipaters with an integral clip, offered by several manufacturers, result in a low cost assembly. When higher power is being handled, a separate clip may be used with larger heatsinks. In order to provide proper pressure, the clip must be specially designed for a particular heatsink thickness and semiconductor package.

Clips are especially popular with plastic packages such as the TO-220 and TO-126. In addition to fast assembly, the clip provides lower interface thermal resistance than other assembly methods when it is designed for proper pressure to bear on the top of the plastic over the die. The TO-220 package usually is lifted up under the die location when mounted with a single fastener through the hole in the tab because of the high pressure at one end.

#### **Machine Screws**

Machine screws, conical washers, and nuts (or sync nuts) can form a trouble-free fastener system for all types of packages which have mounting holes. However, proper torque is necessary. Torque ratings apply when dry; therefore, care must be exercised when using thermal grease to prevent it from getting on the threads as inconsistent torque readings result. Machine screw heads should not directly contact the surface of plastic packages types as the screw heads are not sufficiently flat to provide properly distributed force. Without a washer, cracking of the plastic case may occur.

#### **Self-Tapping Screws**

Under carefully controlled conditions, sheet-metal screws are acceptable. However, during the tapping process with a standard screw, a volcano-like protrusion will develop in the metal being threaded; an unacceptable surface that could increase the thermal resistance may

result. When standard sheet metal screws are used, they must be used in a clearance hole to engage a speednut. If a self tapping process is desired, the screw type must be used which roll-forms machine screw threads.

#### **Rivets**

Rivets are not a recommended fastener for any of the plastic packages. When a rugged metal flange-mount package or EMS module is being mounted directly to a heatsink, rivets can be used provided press-riveting is used. Crimping force must be applied slowly and evenly. Pop-riveting should never be used because the high crimping force could cause deformation of most semiconductor packages. Aluminum rivets are much preferred over steel because less pressure is required to set the rivet and thermal conductivity is improved.

The hollow rivet, or eyelet, is preferred over solid rivets. An adjustable, regulated pressure press is used such that a gradually increasing pressure is used to pan the eyelet. Use of sharp blows could damage the semiconductor die.

#### Solder

Until the advent of the surface mount assembly technique, solder was not considered a suitable fastener for power semiconductors. However, user demand has led to the development of new packages for this application. Acceptable soldering methods include conventional belt-furnace, irons, vapor-phase reflow, and infrared reflow. It is important that the semiconductor temperature not exceed the specified maximum (usually 260°C) or the die bond to the case could be damaged. A degraded die bond has excessive thermal resistance which often leads to a failure under power cycling.

#### **Adhesives**

Adhesives are available which have coefficients of expansion compatible with copper and aluminum.<sup>(5)</sup> Highly conductive types are available; a 10 mil layer has approximately 0.3°C/W interface thermal resistance. Different types are offered: high strength types for non-field serviceable systems or low strength types for field serviceable systems. Adhesive bonding is attractive when case mounted parts are used in wave soldering assembly because thermal greases are not compatible with the conformal coatings used and the greases foul the solder process.

#### **Plastic Hardware**

Most plastic materials will flow, but differ widely in this characteristic. When plastic materials form parts of the fastening system, compression washers are highly valuable to assure that the assembly will not loosen with time and temperature cycling. As previously discussed, loss of contact pressure will increase interface thermal resistance.

#### **FASTENING TECHNIQUES**

Each of the various classes of packages in use requires different fastening techniques. Details pertaining to each type are discussed in following sections. Some general considerations follow.

To prevent galvanic action from occurring when devices are used on aluminum heatsinks in a corrosive atmosphere, many devices are nickel— or gold—plated. Consequently, precautions must be taken not to mar the finish.

Another factor to be considered is that when a copper based part is rigidly mounted to an aluminum heatsink, a bimetallic system results which will bend with temperature changes. Not only is the thermal coefficient of expansion different for copper and aluminum, but the temperature gradient through each metal also causes each component to bend. If bending is excessive and the package is mounted by two or more screws the semiconductor chip could be damaged. Bending can be minimized by:

1. Mounting the component parallel to the heatsink fins to provide increased stiffness.

- 2. Allowing the heatsink holes to be a bit oversized so that some slip between surfaces can occur as temperature changes.

- Using a highly conductive thermal grease or mounting pad between the heatsink and semiconductor to minimize the temperature gradient and allow for movement.

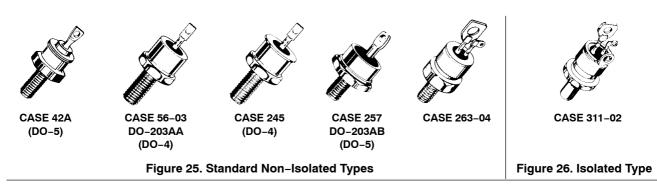

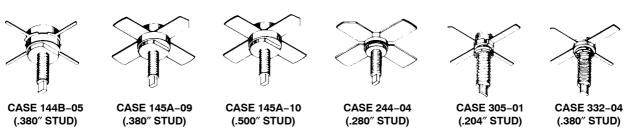

#### Stud Mount

Parts which fall into the stud-mount classification are shown in Figure 24 through Figure 27. Mounting errors with non-insulated stud-mounted parts are generally confined to application of excessive torque or tapping the stud into a threaded heatsink hole. Both these practices may cause a warpage of the hex base which may crack the semiconductor die. The only recommended fastening method is to use a nut and washer; the details are shown in Figure 28.

Figure 27. RF Stripline Opposed Emitter (SOE) Series

A VARIETY OF STUD-MOUNT PARTS

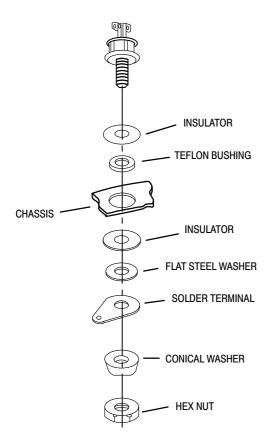

Figure 28. Isolating Hardware Used for a Non-Isolated Stud-Mount Package

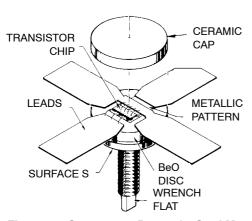

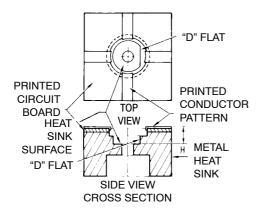

Insulated electrode packages on a stud mount base require less hardware. They are mounted the same as their non-insulated counterparts, but care must be exercised to avoid applying a shear or tension stress to the insulation layer, usually a beryllium oxide (BeO) ceramic. This requirement dictates that the leads must be attached to the circuit with flexible wire. In addition, the stud hex should be used to hold the part while the nut is torqued.

RF transistors in the stud-mount stripline opposed emitter (SOE) package impose some additional constraints because of the unique construction of the package. Special techniques to make connections to the stripline leads and to mount the part so no tension or shear forces are applied to any ceramic – metal interface are discussed in the section entitled "Connecting and Handling Terminals."

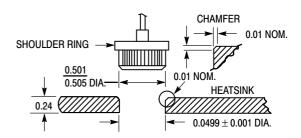

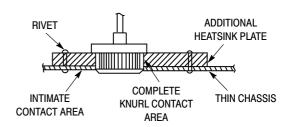

#### **Press Fit**

For most applications, the press-fit case should be mounted according to the instructions shown in Figure 29. A special fixture meeting the necessary requirements must be used.

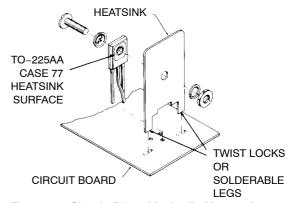

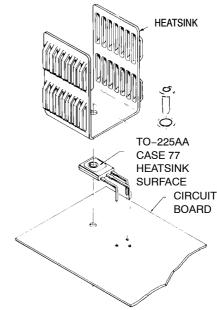

**HEATSINK MOUNTING**

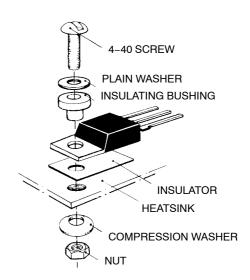

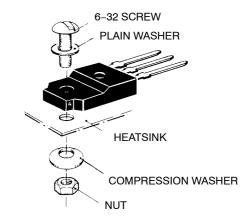

THIN-CHASSIS MOUNTING